### UNIVERSITY OF TWENTE.

# Asynchronous Readers and Writers

A Half-Synchronous Operator

#### Introduction of the \$\psi\$ together with the \$\begin{array}{c}\$ and \$\mathcal{c}\$.

! and ? versus ; and ¿

and ¿using 🗅

Design Level

Semantics of ↓, ¡ and ¿

**Example Application**

The Future

### Introduction, system overview

► Purpose: Asynchronous Writing and Reading.

- Purpose: Asynchronous Writing and Reading.

- In CSP writing over a channel is restricted to two processes interacting synchronously via an action containing the ! and the ?.

- Purpose: Asynchronous Writing and Reading.

- In CSP writing over a channel is restricted to two processes interacting synchronously via an action containing the ! and the ?.

- ▶ Proposal: a half-synchronous action which allows a process to write a value x over a channel c,

- Purpose: Asynchronous Writing and Reading.

- In CSP writing over a channel is restricted to two processes interacting synchronously via an action containing the ! and the ?.

- Proposal: a half-synchronous action which allows a process to write a value x over a channel c,

- without the requirement that the reading processes must be in a state where they can read the value x over a channel c.

- Purpose: Asynchronous Writing and Reading.

- In CSP writing over a channel is restricted to two processes interacting synchronously via an action containing the ! and the ?.

- Proposal: a half-synchronous action which allows a process to write a value x over a channel c,

- without the requirement that the reading processes must be in a state where they can read the value x over a channel c.

- Together with a half-synchronous parallel alphabetised operator.

Advantages of the half-synchronous operator  $\Downarrow$  with half-synchronous actions containing ; or ¿:

Advantages of the half-synchronous operator  $\Downarrow$  with half-synchronous actions containing ; or &:

• it eases the complexity of the design eliminating arguably complex process specifications:

Advantages of the half-synchronous operator  $\Downarrow$  with half-synchronous actions containing ; or &:

- it eases the complexity of the design eliminating arguably complex process specifications:

- it is not necessary to use a buffer process in the model to achieve asynchronous writing and reading,

Advantages of the half-synchronous operator  $\Downarrow$  with half-synchronous actions containing ; or &:

- it eases the complexity of the design eliminating arguably complex process specifications:

- it is not necessary to use a buffer process in the model to achieve asynchronous writing and reading,

- the writes (i) and reads (¿) are asynchronous, which makes it possible to have an order of writes and reads that, if synchronous (!, ?), would lead to a deadlock,

Advantages of the half-synchronous operator  $\Downarrow$  with half-synchronous actions containing ; or &:

- it eases the complexity of the design eliminating arguably complex process specifications:

- it is not necessary to use a buffer process in the model to achieve asynchronous writing and reading,

- the writes (i) and reads (¿) are asynchronous, which

makes it possible to have an order of writes and reads that,

if synchronous (!, ?), would lead to a deadlock,

- by reducing the number of actions involved in this asynchronous writing and reading of the processes, improves the performance of the periodic hard real-time application,

Advantages of the half-synchronous operator  $\Downarrow$  with half-synchronous actions containing ; or &:

- it eases the complexity of the design eliminating arguably complex process specifications:

- it is not necessary to use a buffer process in the model to achieve asynchronous writing and reading,

- the writes (i) and reads (¿) are asynchronous, which

makes it possible to have an order of writes and reads that,

if synchronous (!, ?), would lead to a deadlock,

- by reducing the number of actions involved in this asynchronous writing and reading of the processes, improves the performance of the periodic hard real-time application,

- in a distributed computing system, for example a processor-coprocessor combination, the waiting time of

the processor-coprocessor can be reduced.

UNIVERSITY OF TWENTE. Asynchronous Readers and Writers

Introduction of the \$\psi\$ together with the \$\begin{array}{c}\$ and \$\mathcal{c}\$\$

! and ? versus; and ¿

and susing

Design Level

Semantics of U, ; and ¿

**Example Application**

The Future

### ! and ? versus; and ¿

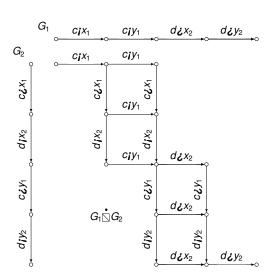

Listing 1: Deadlock due to synchronous writing and reading

$$A = c!x_1 \rightarrow c!y_1 \rightarrow d?x_2 \rightarrow d?y_2 \rightarrow SKIP$$

$$B = c?x_1 \rightarrow d!x_2 \rightarrow c?y_1 \rightarrow d!y_2 \rightarrow SKIP$$

$$AB = A||B$$

### ! and ? versus; and ¿

Listing 1: Deadlock due to synchronous writing and reading

$$A = c!x_1 \rightarrow c!y_1 \rightarrow d?x_2 \rightarrow d?y_2 \rightarrow SKIP$$

$$B = c?x_1 \rightarrow d!x_2 \rightarrow c?y_1 \rightarrow d!y_2 \rightarrow SKIP$$

$$AB = A||B$$

trace: c.x<sub>1</sub>

$$A = c!x_1 \rightarrow c!y_1 \rightarrow d?x_2 \rightarrow d?y_2 \rightarrow SKIP$$

$$B = c?x_1 \rightarrow d!x_2 \rightarrow c?y_1 \rightarrow d!y_2 \rightarrow SKIP$$

$$AB = A||B$$

trace: c.x<sub>1</sub>

Listing 2: No deadlock due to asynchronous writing and reading

$$A=c_1x_1 \rightarrow c_1y_1 \rightarrow d_{\boldsymbol{\zeta}}x_2 \rightarrow d_{\boldsymbol{\zeta}}y_2 \rightarrow SKIP$$

$$B = c : X_1 \rightarrow d : X_2 \rightarrow c : y_1 \rightarrow d : y_2 \rightarrow SKIP$$

$$AB = A \Downarrow B$$

$$A = c!x_1 \rightarrow c!y_1 \rightarrow d?x_2 \rightarrow d?y_2 \rightarrow SKIP$$

$B = c?x_1 \rightarrow d!x_2 \rightarrow c?y_1 \rightarrow d!y_2 \rightarrow SKIP$

$AB = A||B$

trace: c.x<sub>1</sub>

Listing 2: No deadlock due to asynchronous writing and reading

$$A = c_1 x_1 \rightarrow c_1 y_1 \rightarrow d_2 x_2 \rightarrow d_2 y_2 \rightarrow SKIP$$

$B = c_2 x_1 \rightarrow d_1 x_2 \rightarrow c_2 y_1 \rightarrow d_1 y_2 \rightarrow SKIP$

$AB = A \parallel B$

many possible traces, for example:

$$c_1x_1 \rightarrow c_1y_1 \rightarrow c_2x_1 \rightarrow d_1x_2 \rightarrow c_2y_1 \rightarrow d_1y_2 \rightarrow d_2x_2 \rightarrow d_2x_2 \rightarrow SKIP$$

Introduction of the  $\Downarrow$  together with the  $\restriction$  and  $\ifmmode_{i}$

! and ? versus ; and ¿

and ¿using 💆

Design Level

Semantics of ↓,; and ¿

**Example Application**

The Future

## and ¿using 💆

UNIVERSITY OF TWENTE.

AsynchronousReaders and Writers

Introduction of the \$\psi\$ together with the \$\begin{array}{c}\$ and \$\mathcal{c}\$\$

! and ? versus ; and ¿

and ¿using 🗅

### Design Level

Semantics of  $\Downarrow$ ,  $\restriction$  and  $\ifmmode{\iota}\else$

**Example Application**

The Future

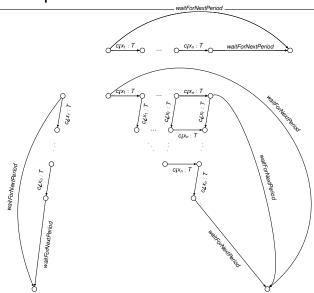

### Design Level

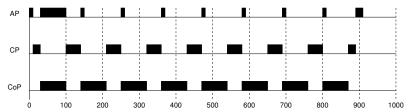

Separation of write/read actions in time

### Design Level

Separation of write/read actions in time Needs a Buffer

Separation of write/read actions in time Needs a Buffer

$A = write.x \rightarrow SKIP$

$B = read.x \rightarrow SKIP$

Buffer = write. $x \rightarrow read.x \rightarrow SKIP$

AB = A|B|Buffer

Separation of write/read actions in time Needs a Buffer

$$A = write.x \rightarrow SKIP$$

$$B = read.x \rightarrow SKIP$$

Buffer = write.

$$x \rightarrow read.x \rightarrow SKIP$$

$$AB = A||B||Buffer$$

$$A = c_i x \rightarrow SKIP$$

$$B = c : X \to SKIP$$

$$AB = A \downarrow B$$

Introduction of the \$\psi\$ together with the \$\begin{array}{c}\$ and \$\begin{array}{c}\$\$ and \$\begin{array}{c}\$\$\$ \$=\$ 1 \end{array}.

! and ? versus ; and ¿

and ¿using 🗅

Design Level

Semantics of U, i and ¿

**Example Application**

The Future

## Semantics of **\$**, ; and ¿

$$\frac{P \overset{c_{i} \times : T}{\longleftrightarrow} P', \ Q_{1} \overset{c_{i} \times : T}{\longleftrightarrow} Q'_{1}, \cdots, Q_{n} \overset{c_{i} \times : T}{\longleftrightarrow} Q'_{n}}{P \Downarrow Q_{1} \Downarrow \cdots \Downarrow Q_{n} \overset{c_{i} \times : T}{\longleftrightarrow} P' \Downarrow Q_{1} \Downarrow \cdots \Downarrow Q_{n} \overset{c_{i} \times : T}{\longleftrightarrow} P' \Downarrow Q'_{1} \Downarrow \cdots \Downarrow Q'_{n}},$$

$$c_{i} \times : T \notin (X, Z)$$

$$\frac{P \overset{c_{\downarrow} x:T}{\longleftrightarrow} P', \ Q_{1} \overset{c_{\downarrow} x:T}{\longleftrightarrow} Q'_{1}, \cdots, Q_{n} \overset{c_{\downarrow} x:T}{\longleftrightarrow} Q'_{n}}{P \Downarrow Q_{1} \Downarrow \cdots \Downarrow Q_{n} \overset{c_{\downarrow} x:T}{\longleftrightarrow} P' \Downarrow Q_{1} \Downarrow \cdots \Downarrow Q'_{n} \overset{c_{\downarrow} x:T}{\longleftrightarrow} P' \Downarrow Q'_{1} \Downarrow \cdots \Downarrow Q'_{n}},$$

$$c_{\downarrow} x: T \notin (X, Z)$$

$$\frac{Q_{i} \overset{c \overset{\boldsymbol{\mathcal{E}} \times : T}{\longrightarrow} Q'_{i}, \ Q_{j} \overset{\boldsymbol{\mathcal{Y}}}{\longrightarrow} Q'_{j}}{Q_{i} \Downarrow Q_{j} \overset{\boldsymbol{\mathcal{Y}}}{\longrightarrow} Q_{i} \Downarrow Q'_{j}}, \ \boldsymbol{\mathcal{Y}} \neq \boldsymbol{\mathcal{C}} \overset{\boldsymbol{\mathcal{E}}}{\longleftarrow} \boldsymbol{\mathcal{X}} : T, \boldsymbol{\mathcal{C}} \overset{\boldsymbol{\mathcal{E}}}{\longleftarrow} \boldsymbol{\mathcal{X}} : T \in (Y_{i} \cdot Y_{j}), \\ \boldsymbol{\mathcal{Y}} \notin (X, Y_{k=1, \cdots n, j \neq k}, Z)$$

$$\frac{P\overset{c_{1}x:T}{\longleftrightarrow}P',\ Q_{1}\overset{c_{2}x:T}{\longleftrightarrow}Q'_{1},\cdots,Q_{n}\overset{c_{2}x:T}{\longleftrightarrow}Q'_{n}}{P\Downarrow Q_{1}\Downarrow\cdots\Downarrow Q_{n}\overset{c_{1}x:T}{\longleftrightarrow}P'\Downarrow Q_{1}\Downarrow\cdots\Downarrow Q_{n}\overset{c_{2}x:T}{\longleftrightarrow}P'\Downarrow Q'_{1}\Downarrow\cdots\Downarrow Q'_{n}},$$

$$C\overset{c_{2}x:T}{\longleftrightarrow}Q'_{i},\ Q_{j}\overset{y}{\to}Q'_{j},$$

$$Q_{i}\overset{c_{2}x:T}{\longleftrightarrow}Q'_{i},\ Q_{j}\overset{y}{\to}Q_{i}\Downarrow Q'_{j},$$

$$y\notin (X,Y_{k=1,\cdots n,j\neq k},Z)$$

$$\frac{P\leadsto P',\ Q_{i}\overset{c_{2}x:T}{\to}Q'_{i}}{P\leadsto P'},\ (\alpha(\leadsto)\cdot(Y_{1},\cdots,Y_{n},Z))=\varnothing$$

$$\frac{P \leadsto P', \ Q_{i}^{c} \overset{\iota \times : T}{\longrightarrow} Q_{i}'}{P \leadsto P'}, \ (\alpha(\leadsto) \cdot (Y_{1}, \cdots, Y_{n}, Z)) = \emptyset$$

$$\frac{Q_{i}^{c} \overset{\iota \times : T}{\longrightarrow} Q_{i}', \ Q_{j}^{c} \overset{\iota \times : T}{\longrightarrow} Q_{j}'}{SKIP}, \ i \neq j$$

### Example

Introduction of the \$\psi\$ together with the \$\begin{array}{c}\$ and \$\begin{array}{c}\$\$ and \$\begin{array}{c}\$\$\$ \$=\$ 1 \end{array}.

! and ? versus ; and ¿

and ¿ using \( \sqrt{}

Design Level

Semantics of ↓,; and ¿

**Example Application**

The Future

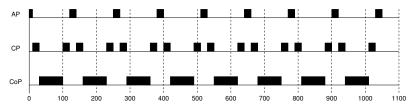

### Case study

Application =

$$c_1 ! x_1 : T \rightarrow c_2 ? y_1 : T \rightarrow \cdots$$

$c_1 ! x_8 : T \rightarrow c_2 ? y_8 : T \rightarrow$

$display_f(y_1, \cdots, y_8) \rightarrow SKIP$

```

Application = c_1 ! x_1 : T \rightarrow c_2 ? y_1 : T \rightarrow

c_1! x_8: T \rightarrow c_2? y_8: T \rightarrow

display_f(y_1, \dots, y_8) \rightarrow SKIP

```

Controller =

$$c_1 ? x_1 : T \rightarrow writeCoProc.x_1 \rightarrow readCoProc.y_1 \rightarrow c_2 ! y_1 : T \rightarrow \dots$$

$$c_1$$

?  $x_8 : T \rightarrow writeCoProc. x_8 \rightarrow readCoProc. y_8 \rightarrow c_2 ! y_8 : T \rightarrow SKIP$

```

Application = c_1 ! x_1 : T \rightarrow c_2 ? v_1 : T \rightarrow

c_1! x_8: T \rightarrow c_2? y_8: T \rightarrow

display_f(v_1, \dots, v_8) \rightarrow SKIP

Controller = c_1 ? x_1 : T \rightarrow writeCoProc.x_1 \rightarrow

readCoProc.y_1 \rightarrow c_2!y_1: T \rightarrow

c_1 ? x_8 : T \rightarrow writeCoProc.x_8 \rightarrow

readCoProc.v_8 \rightarrow c_2!v_8: T \rightarrow SKIP

```

$System_1 = Application_A ||_C Controller$

Application =

$$c_1 : x_1 : T \rightarrow \cdots \rightarrow c_1 : x_8 : T \rightarrow c_2 : y_1 : T \rightarrow \cdots \rightarrow c_2 : y_8 : T \rightarrow display_f(y_1, \cdots, y_8) \rightarrow SKIP$$

Application =

$$c_1 \mid x_1 : T \rightarrow \cdots \rightarrow c_1 \mid x_8 : T \rightarrow c_2 \mid y_1 : T \rightarrow \cdots \rightarrow c_2 \mid y_8 : T \rightarrow display f(y_1, \cdots, y_8) \rightarrow SKIP$$

Controller =

$$c_1 : X_1 : T \rightarrow writeCoProc. x_1 \rightarrow readCoProc. y_1 \rightarrow c_2 : y_1 : T \rightarrow \cdots$$

$$c_1 : X_8 : T \rightarrow writeCoProc. x_8 \rightarrow \cdots$$

$readCoProc.v_8 \rightarrow c_2 i v_8 : T \rightarrow SKIP$

Application =

$$c_1 \mathbf{i} x_1 : T \rightarrow \cdots \rightarrow c_1 \mathbf{i} x_8 : T \rightarrow c_2 \mathbf{i} y_1 : T \rightarrow \cdots \rightarrow c_2 \mathbf{i} y_8 : T \rightarrow display_f(y_1, \cdots, y_8) \rightarrow \mathsf{SKIP}$$

Controller =

$$c_1 : X_1 : T \rightarrow writeCoProc. x_1 \rightarrow readCoProc. y_1 \rightarrow c_2 : y_1 : T \rightarrow ...$$

$$c_1 : X_8 : T \rightarrow writeCoProc. x_8 \rightarrow readCoProc. y_8 \rightarrow c_2 : y_8 : T \rightarrow SKIP$$

$System_2 = Application_A \Downarrow_C Controller$

Introduction of the \$\psi\$ together with the \$\begin{array}{c}\$ and \$\mathcal{c}\$\$

! and ? versus ; and ¿

and susing

Design Level

Semantics of ↓,; and ¿

**Example Application**

The Future

#### Future work:

Index the half-synchronous action such that it is set-wise asynchronous and intra-set-wise synchronous,

- Index the half-synchronous action such that it is set-wise asynchronous and intra-set-wise synchronous,

- ▶ elaborate the graph-theoretical characteristics of \(\sigma\) (VRSP together with the half-synchronous operator),

- Index the half-synchronous action such that it is set-wise asynchronous and intra-set-wise synchronous,

- elaborate the graph-theoretical characteristics of

(VRSP together with the half-synchronous operator), i.e. it is a commutative monoid of consistent graphs,

- Index the half-synchronous action such that it is set-wise asynchronous and intra-set-wise synchronous,

- ▶ elaborate the graph-theoretical characteristics of \( \subseteq \) (VRSP together with the half-synchronous operator), i.e. it is a commutative monoid of consistent graphs,

- implementation in a tool-chain

- Index the half-synchronous action such that it is set-wise asynchronous and intra-set-wise synchronous,

- ▶ elaborate the graph-theoretical characteristics of \( \times \) (VRSP together with the half-synchronous operator), i.e. it is a commutative monoid of consistent graphs,

- implementation in a tool-chain and

- perform a case-study on a periodic hard real-time system.

# Thanks!