# **HIGH-PERFORMANCE PARALLEL INTERFACE -**

# Mechanical, Electrical, and Signalling Protocol Specification

# (HIPPI-PH)

maintenance copy of American National Standard for Information Systems X3.183-1991

March 3, 1993

Secretariat:

Computer & Business Equipment Manufacturers Association

ABSTRACT: The described High-Performance Parallel Interface (HIPPI-PH) is intended as the physical layer of an efficient simplex high-performance point-to-point interface for transmitting digital data at peak data rates of 800 or 1600 Mbit/s between data-processing equipment using multiple twisted-pair copper cabling at distances up to 25 m.

# NOTE:

This document is an X3T11 maintenance copy of American National Standard X3.183-1991. A list of the proposed changes since approval of the standard is included. Some or all of these changes may be included in a future erratum, amendment, interpretation, or revision to the standard. The committee lists included in the approved standard, and some other boilerplate, have been omitted in this draft. For current information on the status of this document contact the individual shown below.

POINTS OF CONTACT:

Roger Cummings (X3T11 Chairman) Storage Technology Corporation 2270 South 88th Street Louisville, CO 80028-0268 (303) 661-6357, FAX (303) 684-8196 E-mail: Roger\_Cummings@Stortek.com

Don Tolmie (HIPPI-PH Technical Editor) Los Alamos National Laboratory C-5, MS-B255 Los Alamos, NM 87545 Carl Zeitler (X3T11 Vice-Chairman) IBM Corporation, MS 9440 11400 Burnet Road Austin, TX 78758 (512) 838-1797, FAX (512) 838-3822 E-mail: zeitler@ausvm6.vnet.ibm.com (505) 667-5502, FAX (505) 665-7793 E-mail: det@lanl.gov Proposed changes to ANSI X3.183-1991 - (and which have been incorporated in this draft)

Proposed technical changes are preceded with (T), proposed editorial changes are preceded with (E).

Rev 8.2, March 3, 1993 version - To date all of the proposed changes are editorial (E).

- 1. (E) Change 2.1, line 1, from "For the purposes of..." to "For the purpose of...".

- 2. (E) Change 2.1.7, last line, from "...or by a upper..." to "...or by an upper...".

- 3. (E) Change 2.2, last line, change "...English meanings." to "...English meaning.".

- 4. (E) Deleted an extra space after the period in some of the primitive names, e.g., "PH\_HANGUP. Request". This affected line 5 of 4.5.1, line 12 of 4.8.2, line 1 of 4.8.4, line 1 of 4.9.2, line 1 of 4.10.2, line 3 of 4.10.3, line 5 of 4.10.4, and last line of 4.12.1.

- 5. (E) In 4.6.2, line 5/6, moved the period after "ANSWER" to before "Request".

- (E) In 4.12.3, lines 6/7, moved "A change in the INTERCONNECT signal" to the end of the previous line instead of indenting it.

- 7. (E) In 5.1.5, added a period after the sentence "All addition is modulo 2", in two places.

- 8. (E) Capitalized the words "source" and "destination in figures 17 and 18, S1170, S1230, S1260, D1670, D1770, D1630, and D1750.

- 9. (E) In 8.1.3, 8.2.2, and 8.5 added a space between the number and the  $\Omega$ .

- 10. (E) In 8.2.1, line 2, change "...voltage shall be meet..." to "...voltage shall meet...".

- 11. (E) In B.6, paragraph 2, change "Figure B.4" to "Figure B.3".

- 12. (E) In B.6, paragraph 3, change "figure B.5" to "figure B.4".

- 13. (E) In E.2, add a space between the numeric value and the units, (m, cm, ft, in).

- 14. (E) In the Index, change "int" to "Introduction" Introduction" in four places. Delete "(int = Introduction)".

# Contents

# Page

| Fore  | eword                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                         | iv                                                          |  |  |

|-------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Intro | oductio                                                                                        | n                                                                                                                                                                                                                                                                                                                                                                                                       | v                                                           |  |  |

| 1     | Scope1                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |  |

| 2     | Definitions and conventions1                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |  |

| 3     | HIPPI :<br>3.1<br>3.2                                                                          | structure<br>Configuration characteristics<br>Logical framing hierarchy                                                                                                                                                                                                                                                                                                                                 | 2                                                           |  |  |

| 4     | Service<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12 | e interface<br>Service primitives<br>Sequences of primitives<br>Service primitives summary<br>Operational sequences<br>Initiate connection service primitives<br>Complete the connection service primitives<br>Flow control service primitives<br>Packet service primitives<br>Data transfer service primitives<br>Hangup service primitives<br>Control service primitives<br>Status service primitives | 2<br>3<br>3<br>4<br>4<br>5<br>7<br>7<br>8                   |  |  |

| 5     | Interfac<br>5.1<br>5.2<br>5.3<br>5.4                                                           | ce format and signals.<br>Physical framing hierarchy.<br>Data rate options.<br>Usage of signals.<br>Error detection.                                                                                                                                                                                                                                                                                    | .10<br>.11<br>.11                                           |  |  |

| 6     | State to<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                             | ransitions<br>State exit<br>Interlocks<br>Source READY pseudo-code<br>Destination READY pseudo-code<br>Source pseudo-code<br>Destination pseudo-code                                                                                                                                                                                                                                                    | .14<br>.14<br>.14<br>.14<br>.15                             |  |  |

| 7     | Timing<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9                          | Source CLOCK signal<br>Destination CLOCK signal<br>DATA BUS and PARITY BUS timing<br>Source control signals<br>I-Field information<br>LLRC<br>Destination control signals<br>Source wait gaps<br>Destination wait gaps                                                                                                                                                                                  | .21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22 |  |  |

|       | 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8                                           | al characteristics<br>Differential circuit characteristics<br>INTERCONNECT signal characteristics<br>Ground signals<br>Reserved signals<br>Cable specifications<br>Cable grounding<br>Connector specifications<br>Connector pin assignments<br>al Index                                                                                                                                                 | .23<br>.24<br>.24<br>.24<br>.24<br>.25<br>.25<br>.25        |  |  |

# Tables

| 1    | Data rate options11                         |

|------|---------------------------------------------|

| 2    | Connector pin assignments26                 |

| Figu | ures                                        |

| 1    | Control hierarchyvi                         |

| 2    | Logical framing hierarchy2                  |

| 3    | HIPPI-PH service interface2                 |

| 4    | Initiate the connection service primitives4 |

| 5    | Complete the connection service primitives4 |

| 6    | Flow control service primitives5            |

| 7    | Packet service primitives6                  |

| 8    | Data transfer service primitives7           |

| 9    | Hangup service primitives7                  |

| 10   | Control service primitives                  |

| 11   | Status service primitives9                  |

| 12   | Physical framing hierarchy10                |

| 13   | Interface signal summary10                  |

| 14   | Data packing12                              |

| 15   | Source READY flow diagram14                 |

| 16   | Destination READY flow diagram14            |

| 17   | Source flow diagram16                       |

| 18   | Destination flow diagram19                  |

| 19   | Source driven signals at the Source21       |

| 20   | Source driven signals at the Destination21  |

| 21   | Differential circuit23                      |

| 22   | INTERCONNECT circuit                        |

| 23   | Cable connector – tabs27                    |

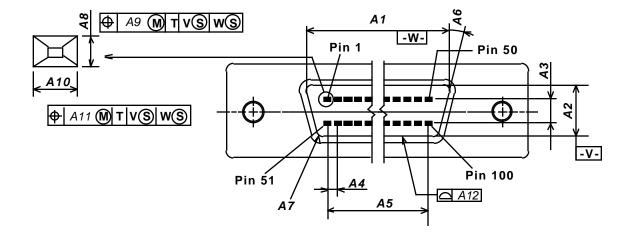

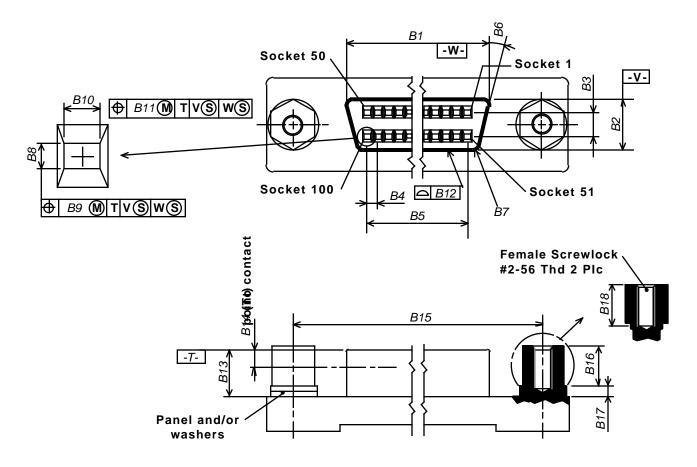

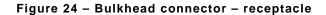

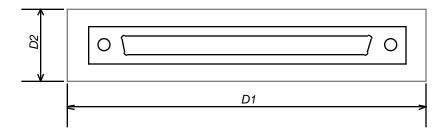

| 24   | Bulkhead connector – receptacle             |

# Annexes

| Α | Wavefo                              | orm examples (informative)                       |     |  |  |  |

|---|-------------------------------------|--------------------------------------------------|-----|--|--|--|

|   | A.1                                 | Introduction                                     |     |  |  |  |

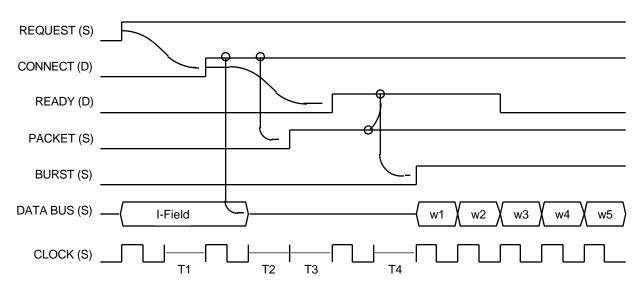

|   | A.2                                 | Connection and start packet                      |     |  |  |  |

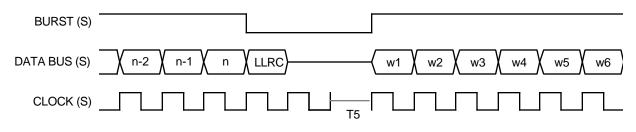

|   | A.3                                 | End burst, start burst                           |     |  |  |  |

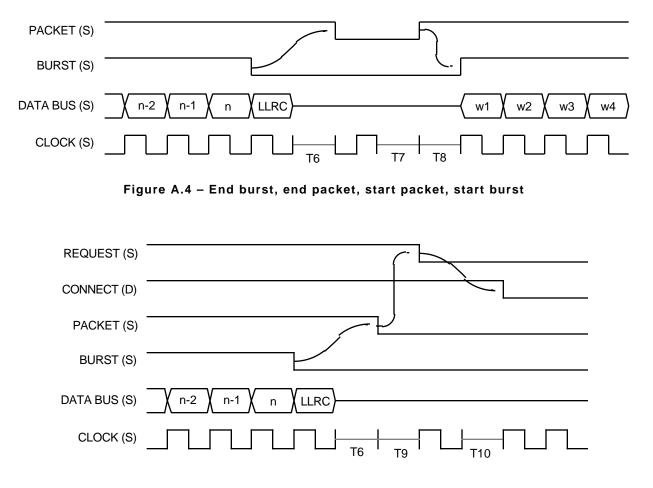

|   | A.4                                 | End burst, end packet, start packet, start burst |     |  |  |  |

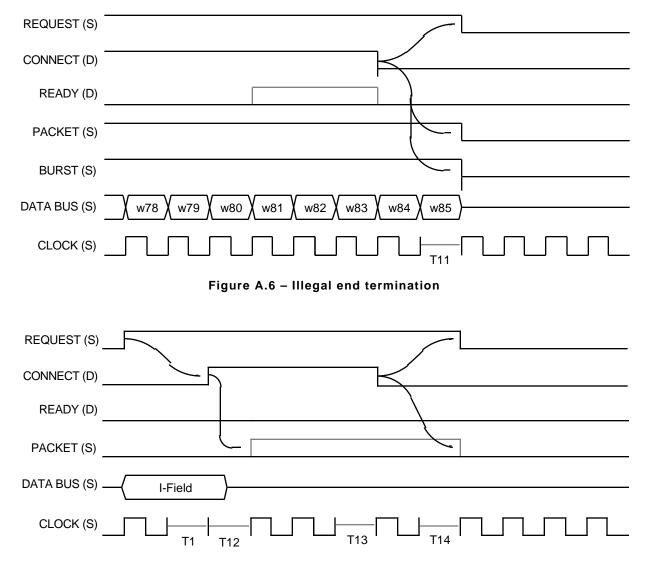

|   | A.5                                 | End burst, end packet, disconnect                |     |  |  |  |

|   | A.6                                 | Illegal end termination                          | .32 |  |  |  |

|   | A.7                                 | Rejected connection sequence                     | .32 |  |  |  |

|   | A.8                                 | Aborted connection sequence                      | .33 |  |  |  |

| В | Implem                              | nentation suggestions (informative)              | .34 |  |  |  |

|   | <b>B.1</b>                          | Data rate option control                         | .34 |  |  |  |

|   | B.2                                 | Source READY counter                             |     |  |  |  |

|   | B.3                                 | I-Field sampling                                 |     |  |  |  |

|   | B.4                                 | Short bursts                                     |     |  |  |  |

|   | B.5                                 | Switching and the I-Field                        |     |  |  |  |

|   | B.6                                 | Byte ordering                                    | .35 |  |  |  |

| С | Error c                             | hecking (informative)                            | .36 |  |  |  |

|   | C.1                                 | Byte parity                                      |     |  |  |  |

|   | C.2                                 | LLRC                                             |     |  |  |  |

|   | C.3                                 | Burst length check                               |     |  |  |  |

|   | C.4                                 | Sample LLRC circuit                              | .36 |  |  |  |

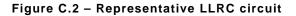

| D | Propad                              | ation delay calculation example (informative)    | .38 |  |  |  |

| _ | D.1                                 | CLOCK                                            |     |  |  |  |

|   | D.2                                 | Loading data                                     | .38 |  |  |  |

|   | D.3                                 | Cable skew                                       | .38 |  |  |  |

|   | D.4                                 | Setup time                                       | .38 |  |  |  |

|   | D.5                                 | Hold time                                        |     |  |  |  |

|   | D.6                                 | Tuning delay                                     | .38 |  |  |  |

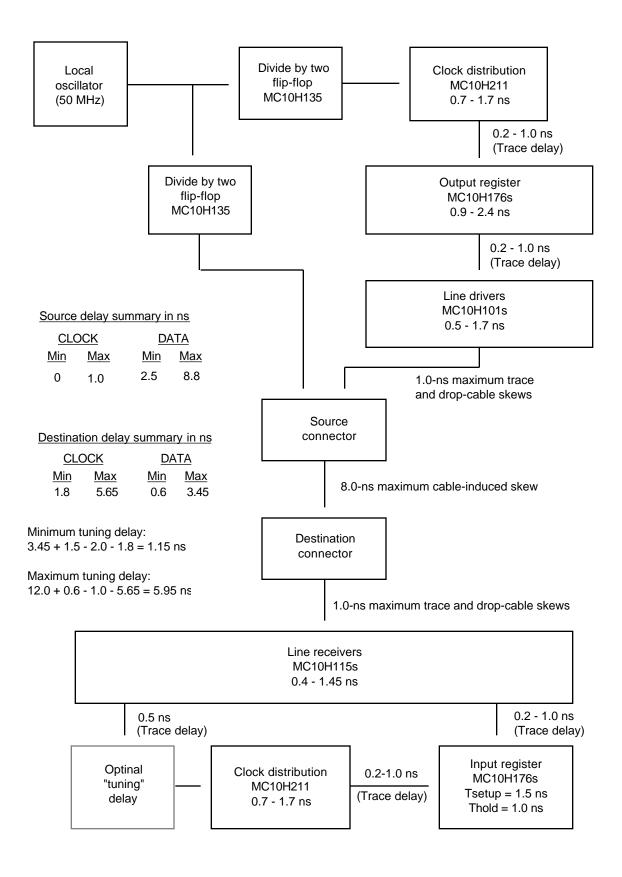

| Е | E Component options (informative)40 |                                                  |     |  |  |  |

|   | E.1                                 | Cable availability and color coding              |     |  |  |  |

|   | E.2                                 | Cable lengths                                    | .40 |  |  |  |

|   | E.3                                 | Connector alignment guide                        | .40 |  |  |  |

|   | E.4                                 | Maximum connector footprint                      |     |  |  |  |

|   | E.5                                 | Connector availability                           |     |  |  |  |

|   | E.6                                 | Line driver and receiver availability            | .40 |  |  |  |

**Foreword** (This Foreword is not part of American National Standard X3.183-1991.)

This standard defines the mechanical, electrical, and signalling protocol specifications of an efficient simplex high-performance point-to-point interface, called the <u>High-Performance Parallel Interface</u> (HIPPI-PH). The -PH abbreviation stands for "physical" layer. This interface was previously named the "High-Speed Channel (HSC)". The name was changed October, 1989, to avoid infringing on an existing trademark, and the abbreviation was changed April, 1990, from HPPI to HIPPI to avoid another trademark.

The HIPPI-PH is designed for transmitting digital data at peak data rates of 800 or 1600 Mbit/s between data-processing equipment using multiple twisted-pair copper cabling at distances up to 25 meters. This standard responds to an industry market need (expressed both by users and manufacturers) to standardize the interconnection of data processing equipments at these data rates.

The HIPPI-PH signalling protocol is designed to be distance independent, allowing the average data rate to approach the peak data rate, even over distances longer than specified for the HIPPI-PH.

This standard was developed by Task Group X3T9.3 of Accredited Standards Committee X3 during 1987 and 1988. The standards approval process started in early 1989.

The HIPPI Framing Protocol (HIPPI-FP) is an upper-layer protocol for the HIPPI-PH.

The American convention of numbering is used i.e., the period is used as the decimal point, and four digit numbers are contiguous. This is equivalent to the ISO convention of a comma for the decimal point, and a space separating thousands and higher multiples.

| ISO         | <u>American</u> |

|-------------|-----------------|

| 0,6         | 0.6             |

| 1 600       | 1600            |

| 1 323 462,9 | 1,323,462.9     |

This document includes annexes which are informative and are not considered part of the standard.

Requests for interpretation, suggestions for improvement or addenda, or defect reports are welcome. They should be sent to the X3 Secretariat, Computer and Business Equipment Manufacturers Association, 1250 Eye Street, NW, Suite 200, Washington, DC 20005.

This standard was processed and approved for submittal to ANSI by Accredited Standards Committee on Information Processing Systems, X3. Committee approval of the standard does not necessarily imply that all committee members voted for approval. At the time it approved this standard, the X3 Committee had the following members:

(List of X3 Committee members included in published standard)

Subcommittee X3T9 on Computer Input/Output Interfaces, which reviewed this standard, had the following members:

(List of X3T9 committee members included in published standard)

Task Group X3T9.3 on Device Level Interfaces, which developed this standard, had the following participants:

(Lis tof X3T9.3 committee participants included in published standard)

# Introduction

This High-Performance Parallel Interface, Mechanical, Electrical, and Signalling Protocol Specification (HIPPI-PH) American National Standard defines the physical layer of an efficient simplex high-performance point-to-point interface operating at speeds of 800 or 1600 Mbit/s. The -PH abbreviation stands for "physical layer".

Characteristics of this HIPPI physical layer interface include:

Point-to-point connections use one or two copper twisted-pair cables for distances of up to 25 m.

- The HIPPI-PH is a simplex interface, capable of transferring data in one direction only. Two HIPPI-PHs may be used to implement a full-duplex interface.

Data transfers are performed and flow controlled in increments of bursts, each burst normally containing 256 words.

- Signalling and control sequences are kept simple, and a look-ahead flow control is used, to allow average transfer rates for large file transfers to approach the peak transfer rate, even over distances longer than specified for the HIPPI-PH cables.

– The HIPPI-PH provides support for low-latency, real-time, and variable size packet transfers.

- The HIPPI-PH is designed to facilitate use in a circuit-switched environment. In support of this feature, a limited information field is available for subdevice addressing or other nonspecified control functions during the connection phase of operation. One round-trip cable delay is required to establish or terminate a connection.

- The HIPPI-PH is also designed to transmit multiple packets after a connection has been established. No round-trip cable delays are required between packets.

The information in the document is organized as follows:

- Clause 1 provides the introductory material.

- Clause 2 provides a glossary and editorial conventions.

- Clause 3 gives an overview of the HIPPI structure and logical organization.

– Clause 4 specifies the services provided by the HIPPI-PH to station management and upper-layer protocols.

- Clause 5 specifies the interface format and the definitions of the signals used in the interface.

- Clause 6 specifies control sequences, using pseudo-code and flow diagrams, required to implement the information transfers.

- Clause 7 provides detailed timing information.

- Clause 8 specifies the electrical and mechanical connections defined by this standard. These specifications cover drivers, receivers, line termination, logic levels, connectors, and cable parameters.

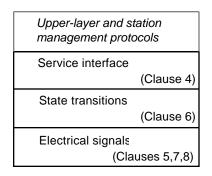

Figure 1 shows the interrelationship of the different clauses of the document. The upper-layer protocols and station management protocols are not covered in this standard.

Figure 1 – Control hierarchy

American National Standard for Information Systems –

# High-Performance Parallel Interface – Mechanical, Electrical, and Signalling Protocol Specification (HIPPI-PH)

# 1 Scope

This American National Standard provides the mechanical, electrical, and signalling protocol specifications for an efficient simplex high-performance point-to-point interface between pieces of data-processing equipment.

The interface described in this document can be operated at peak data rates of 800 or 1600 Mbit/s, over distances of up to 25 m by means of copper cabling. A distance-independent signalling protocol allows the average data rates to approach the peak data rates, even over distances longer than specified for the HIPPI-PH.

The purpose of this American National Standard is to facilitate the development and use of computer systems by providing a common interface at the physical and data framing layers. HIPPI-PH provides an efficient interconnection between computers, high-performance display systems, and high-performance, intelligent block-transfer peripherals. It is optimized for large block transfers.

# 2 Definitions and conventions

#### 2.1 Definitions

For the purpose of this standard, the following definitions apply.

**2.1.1 burst:** A group of words, sent during contiguous CLOCK periods. A burst may be sent by the Source for each READY indication received from the Destination. Bursts contain 1 to 256 words. Bursts that contain less than 256 words are called short bursts. A packet contains no more than one short burst. A short burst will be either the first or last burst of a packet.

**2.1.2 connection:** Condition of the HIPPI-PH when data transfers from Source to Destination are possible.

**2.1.3 Destination:** The equipment that receives the data.

**2.1.4 I-Field:** A 32-bit information field sent as part of the sequence of operations establishing a connection from a Source to a Destination. The contents of the I-Field are defined by an upper-layer protocol and are not defined in this standard.

**2.1.5** length/longitudinal redundancy checkword (LLRC): A single word that is sent on the DATA BUS from Source to Destination after each burst.

**2.1.6 optional:** Features that are not required by the standard. However, if any optional feature defined by the standard is implemented, it shall be implemented according to the standard.

**2.1.7 packet:** A data set sent from Source to Destination. A packet is composed of one or more bursts. The HIPPI-PH specification does not limit the maximum packet size, but a maximum size may be imposed by a given HIPPI-PH implementation, or by an upper-layer protocol.

**2.1.8** service interface (SI): The means by which the HIPPI-PH provides services to upper-layer protocols.

**2.1.9 Source**: The equipment that transmits the data.

**2.1.10 state:** The current condition of the HIPPI-PH, excluding transitions, as indicated by the control signals.

**2.1.11** station management (SMT): The supervisory entity that monitors and controls the HIPPI-PH.

**2.1.12 upper-layer protocol (ULP):** The protocols above the service interface. These could be done in hardware or software, or they could be distributed between the two.

**2.1.13 wait:** Wait is every CLOCK period when there is no valid information on the DATA BUS. Some wait times are required by the HIPPI-PH signalling protocol; others may be the result of flow control or upper-layer protocol operations.

**2.1.14 word:** A unit of information, consisting of 32 or 64 bits, matching the DATA BUS width, and transferred from the Source to the Destination during a CLOCK period.

#### 2.2 Editorial conventions

In this standard, certain terms that are proper names of signals or similar terms are printed in upper case to avoid possible confusion with other uses of the same words (e.g., REQUEST, CONNECT, BURST). Any lower case uses of these words have the normal technical English meaning.

A number of conditions, sequences parameters, events, states, or similar terms are printed with the first letter of each word in upper case and the rest lower case (e.g., Source, Destination). Any lower case uses of these words have the normal technical English meaning.

# 3 HIPPI structure

# 3.1 Configuration characteristics

The HIPPI-PH has been designed in a modular fashion to support different peak bandwidth requirements.

#### 3.1.1 800 Mbit/s

An HIPPI-PH with a DATA BUS width of 32-bit words provides 800 Mbit/s data transfer rates.

#### 3.1.2 1600 Mbit/s

An HIPPI-PH with a DATA BUS width of 64-bit words provides 1600 Mbit/s data transfer rates.

# 3.2 Logical framing hierarchy

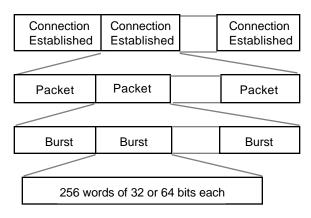

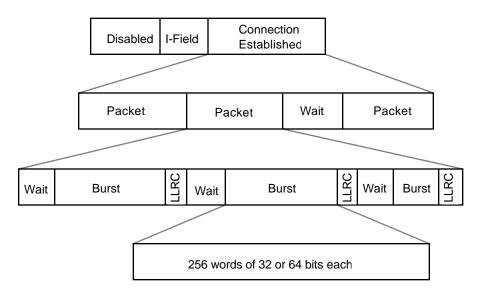

Figure 2 shows the basic organization of the information on the HIPPI-PH.

Once a connection is established a packet (or multiple packets) can be sent from the Source to the Destination. Each packet shall contain one or more bursts. Bursts shall contain 1 to 256 words. Bursts that contain less than 256 words are called short bursts. A packet shall contain no more than one short burst. A short burst shall be either the first or last burst of a multi-burst packet.

Figure 2 – Logical framing hierarchy

# 4 Service interface

This clause specifies the services provided by HIPPI-PH. The intent is to allow ULPs to operate correctly with this HIPPI-PH. How many of the services described herein are chosen for a given implementation is up to that implementor; however, a set of HIPPI-PH services must be supplied sufficient to satisfy the ULP(s) being used. The services as defined herein do not imply any particular implementation, or any interface.

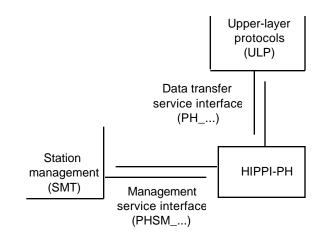

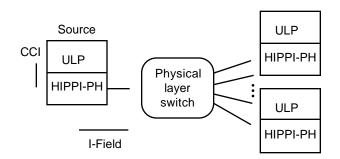

Figure 3 shows the relationship of the HIPPI-PH interfaces.

Figure 3 – HIPPI-PH service interface

# 4.1 Service primitives

The primitives, in the context of the state transitions in clause 5, are declared required or optional. Additionally, parameters are either required, conditional, or optional. All of the primitives and parameters are considered as required except where explicitly stated otherwise.

HIPPI-PH service primitives are of four types.

- *Request primitives* are issued by a service user to initiate a service provided by the HIPPI-PH. In this standard, a second Request primitive of the same name shall not be issued until the Confirm for the first request is received.

-Confirm primitives are issued by the HIPPI-PH to acknowledge a Request.

- Indicate primitives are issued by the HIPPI-PH to notify the service user of a local event. This primitive is similar in nature to an unsolicited interrupt. Note that the local event may have been caused by a service Request. In this standard, a second Indicate primitive of the same name shall not be issued until the Response for the first Indicate is received.

- *Response primitives* are issued by a service user to acknowledge an Indicate.

# 4.2 Sequences of primitives

The order of execution of service primitives is not arbitrary. Logical and time sequence relationships exist for all described service primitives. Time sequence diagrams are used to illustrate a valid sequence. Other valid sequences may exist. The sequence of events between peer users across the user/provider interface is illustrated. In the time sequence diagrams the HIPPI-PH users are depicted on either side of the vertical bars while the HIPPI-PH acts as the service provider.

# 4.3 Service primitives summary

Initiate a Connection PH\_RING.Request (CCI) PH\_RING.Confirm PH\_RING.Indicate (CCI) PH\_RING.Response

Complete the Connection PH\_ANSWER.Request (Accept/Reject) PH\_ANSWER.Confirm PH\_ANSWER.Indicate (Accept/Reject) PH\_ANSWER.Response

Flow Control PH\_FLOW.Request PH\_FLOW.Confirm PH\_FLOW.Indicate (Enabled) PH\_FLOW.Response

# Packet Control

PH\_PACKET.Request (Begin/End) PH\_PACKET.Confirm (Accept/Reject) PH\_PACKET.Indicate (Begin/End,Status) PH\_PACKET.Response

#### **Burst Transfer**

PH\_TRANSFER.Request (Length,Burst) PH\_TRANSFER.Confirm (Accept/Reject) PH\_TRANSFER.Indicate (Status,Length,Burst) PH\_TRANSFER.Response

Terminate the Connection PH\_HANGUP.Request PH\_HANGUP.Confirm PH\_HANGUP.Indicate PH\_HANGUP.Response

Control Interface PHSM\_CONTROL.Request (Parameter\_List) PHSM\_CONTROL.Confirm (Status,Status\_List)

Interface Status PHSM\_STATUS.Request PHSM\_STATUS.Confirm (Status) PHSM\_STATUS.Indicate PHSM\_STATUS.Response

# 4.4 Operational sequences

Primitives issued by the ULP shall be serviced by the HIPPI-PH in the sequences defined in the state transitions of clause 6. An implementation may present the HIPPI-PH with multiple requests for services, but the HIPPI-PH shall service the requests one at a time.

The following sequence of service primitives is an example of normal operation of the HIPPI-PH.

#### 4.4.1 Enable the interface

The interface may be enabled using whatever implementation dependent enabling method, if any, is specified.

#### 4.4.2 Initiate a connection

PH\_RING primitives shall be used to initiate a connection from the Source to the Destination. The Connection Control Information (CCI) may be used for non-specified control functions.

#### 4.4.3 Complete the connection

PH\_ANSWER primitives shall be used to establish or reject the connection.

#### 4.4.4 Enable Destination reception

When it is ready, the Destination ULP may use the PH\_FLOW.Request primitive to indicate that it is willing to accept bursts from the HIPPI-PH.

#### 4.4.5 Start a packet

PH\_PACKET (Begin) primitives shall be used to indicate the start of a packet.

#### 4.4.6 Send burst

PH\_TRANSFER primitives shall be used to transfer one burst of a packet.

#### 4.4.7 Send more bursts

More bursts may be sent for this packet by returning to 4.4.6.

#### 4.4.8 Terminate the packet

PH\_PACKET (End) primitives shall be used to indicate the end of a packet.

#### 4.4.9 Send more packets

More packets may be sent by returning to 4.4.5.

#### 4.4.10 Terminate the connection

The Source or Destination may terminate the connection by using the PH\_HANGUP primitives. Note that dedicated point-to-point HIPPI-PHs may never need to terminate the connection once it is established, or only terminate the connection as an error recovery process. See the cautionary note in 5.3.6.

#### 4.4.11 Initiate another connection

Return to 4.4.2 to initiate another connection.

X3T9.3 maintenance copy of ANSI X3.183-1991

# 4.5 Initiate connection service primitives

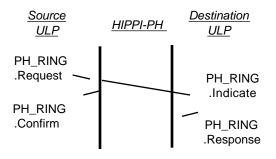

Figure 4 is a diagram of these primitives. They shall be used to request that a connection be established between the Source and Destination.

# Figure 4 – Initiate the connection service primitives

# 4.5.1 PH\_RING.Request

Issued by the Source ULP to request establishment of a connection from the Source to the Destination. In the case where a previous connection attempt did not complete with a PH\_ANSWER.Indicate, and was aborted with a Source ULP issued PH\_HANGUP.Request, the Source must wait a time T1 before initiating another connection. T1 shall be a round-trip propagation delay plus appropriate action time. No assumptions are made as to where or how the timer is implemented. It may be done in the ULP or the HIPPI-PH. The timer may be implemented with hardware, software, or a mixture of the two. The default value of T1 shall be approximately 2 ms.

Semantics - PH\_RING.Request (CCI)

The CCI parameter is a 32-bit field that may be used for non-specified control operations for the connection establishment.

Issued – The Source ULP issues this primitive to the HIPPI-PH when a connection to a Destination ULP is required.

Effect – The HIPPI-PH shall initiate a connection.

# 4.5.2 PH\_RING.Confirm

This primitive acknowledges the PH\_RING.Request from the Source ULP.

Semantics - PH\_RING.Confirm

Issued – The HIPPI-PH shall issue this primitive to the Source ULP to acknowledge a PH\_RING.Request.

Effect - Unspecified

# 4.5.3 PH\_RING.Indicate

This primitive indicates to the Destination ULP an attempt by a Source ULP to establish a connection.

Semantics – PH\_RING.Indicate (CCI)

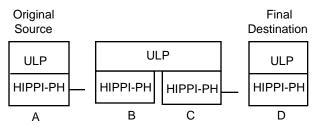

The CCI parameter is a 32-bit field that may be used for non-specified control operations for connection establishment. This CCI may be different from the CCI supplied by the PH\_RING.Request primitive due to the action of intermediate devices, such as switches, between the Source and Destination.

Issued – The HIPPI-PH shall issue this primitive to the Destination ULP when it has received a connection request.

Effect – The Destination ULP should accept or reject the connection request.

# 4.5.4 PH\_RING.Response

This primitive acknowledges the PH\_RING.Indicate from the HIPPI-PH.

Semantics – PH\_RING.Response

Issued – The Destination ULP issues this primitive to acknowledge receipt of the PH\_RING.Indicate.

Effect – The HIPPI-PH is enabled to issue another PH\_RING.Indicate.

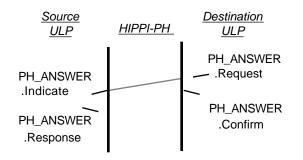

# 4.6 Complete the connection service primitives

Figure 5 is a diagram of these primitives. To respond to a connection request, the PH\_ANSWER primitives shall be used.

Figure 5 – Complete the connection service primitives

# 4.6.1 PH\_ANSWER.Request

This primitive is issued by the Destination ULP in response to the PH\_RING primitives to instruct the HIPPI-PH to reject or establish a connection.

Semantics – PH\_ANSWER.Request (Accept/Reject)

The Accept/Reject parameter instructs the HIPPI-PH to complete the connection or to reject it.

Issued – The Destination ULP should issue this primitive to the HIPPI-PH in response to a PH\_RING.Indicate.

Effect – The HIPPI-PH shall complete the connection if the Accept parameter is used. If the Reject parameter is used, the HIPPI-PH may either do nothing (in which case the Source ULP shall not receive a PH\_ANSWER .Indicate), or perform a short connection sequence (in which case the Source ULP shall receive a PH\_ANSWER .Indicate with the Reject parameter).

#### 4.6.2 PH\_ANSWER.Confirm

This primitive acknowledges the PH\_ANSWER.Request from the Destination ULP.

Semantics – PH\_ANSWER.Confirm

Issued – The HIPPI-PH shall issue this primitive to the Destination ULP to acknowledge a PH\_ANSWER .Request.

Effect – Unspecified

#### 4.6.3 PH\_ANSWER.Indicate

This primitive indicates to the Source ULP that the connection has been accepted or rejected.

Semantics – PH\_ANSWER.Indicate (Accept/Reject)

If the Accept parameter is used, the connection has been accepted and is available for data transfer. If the Reject parameter is used, the connection has been rejected and the interface is available for another PH\_RING.Request.

Issued – The HIPPI-PH shall issue this primitive to the Source ULP when it has determined the status of the connection request.

Effect – The connection sequence is complete.

#### 4.6.4 PH\_ANSWER.Response

This primitive acknowledges the PH\_ANSWER.Indicate from the HIPPI-PH.

Semantics - PH\_ANSWER.Response

Issued – The Source ULP issues this primitive to acknowledge receipt of the PH\_ANSWER.Indicate.

Effect – The HIPPI-PH is enabled to issue another PH ANSWER.Indicate.

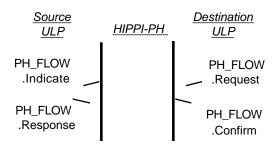

#### 4.7 Flow control service primitives (optional)

Figure 6 is a diagram of these primitives. These primitives are optional, and may be used to pass flow control information between the HIPPI-PH and the Source and Destination ULPs.

The Flow Control service primitives are used by the Destination ULP to inform the HIPPI-PH that it is willing to accept a burst in the form of the PH\_TRANSFER.Indicate.

Figure 6 – Flow control service primitives

#### 4.7.1 PH\_FLOW.Request

This primitive is issued by the Destination ULP to tell the HIPPI-PH that it is ready to accept a burst from the HIPPI-PH.

Semantics - PH\_FLOW.Request

Issued – The Destination ULP issues this primitive to the HIPPI-PH when it is ready to receive bursts.

Effect – The HIPPI-PH shall be enabled to send another burst to the Destination ULP. Each PH\_FLOW.Request enables an additional PH\_TRANSFER.Indicate.

# 4.7.2 PH\_FLOW.Confirm

This primitive acknowledges the PH\_FLOW.Request from the Destination ULP.

Semantics - PH\_FLOW.Confirm

Issued – The HIPPI-PH shall issue this primitive to the Destination ULP to acknowledge a PH\_FLOW.Request.

Effect - Unspecified

#### 4.7.3 PH\_FLOW.Indicate

This primitive notifies the Source ULP that it can send a burst. It shall indicate to the Source ULP the current number of available bursts that the HIPPI-PH is willing to accept.

Semantics – PH\_FLOW.Indicate (Enabled)

The Enabled parameter shall be the current number of bursts that the HIPPI-PH is willing to accept. The range is implementation dependent.

Issued – The HIPPI-PH shall attempt to issue this primitive to the Source ULP every time it receives an indication that another burst can be transmitted.

Effect - Unspecified

#### 4.7.4 PH\_FLOW.Response

This primitive acknowledges the PH\_FLOW.Indicate from the HIPPI-PH.

Semantics – PH\_FLOW.Response

Issued – The Source ULP issues this primitive to acknowledge receipt of the PH\_FLOW.Indicate.

Effect – The HIPPI-PH is enabled to issue another PH\_FLOW.Indicate.

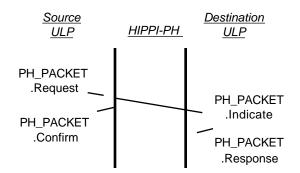

# 4.8 Packet service primitives

Figure 7 is a diagram of these primitives. They shall be used to delimit one or more bursts into entities called packets.

Figure 7 – Packet service primitives

# 4.8.1 PH\_PACKET.Request

This primitive is issued by the Source ULP to delimit one or more bursts into a packet entity.

Semantics - PH\_PACKET.Request (Begin/End)

The parameter marks either the beginning or the end of the packet.

Issued – The Source ULP issues this primitive to the HIPPI-PH to delimit one or more bursts into a packet.

Effect – Upon receipt of a Begin parameter, the HIPPI-PH shall mark the start of a packet. Upon receipt of an End parameter, the HIPPI-PH shall mark the end of a packet.

# 4.8.2 PH\_PACKET.Confirm

This primitive acknowledges the PH\_PACKET.Request from the Source ULP.

Semantics - PH\_PACKET.Confirm (Accept/Reject)

The parameter denotes whether or not the primitive was accepted by the HIPPI-PH. The PH\_PACKET.Request primitive may have been issued by the ULP along with other primitives, e.g., RING.Request. If the connection sequence fails, then the packet delimiter would not be inserted and this PH\_PACKET.Confirm primitive would indicate Reject.

Issued – The HIPPI-PH shall issue this primitive to the Source ULP to acknowledge a PH\_PACKET.Request.

Effect - Unspecified

# 4.8.3 PH\_PACKET.Indicate

This primitive indicates to the Destination ULP that a packet delimiter has been received from the Source ULP.

Semantics – PH\_PACKET.Indicate (Begin/End, Status)

The Begin/End parameter indicates either the beginning or the end of the packet.

The Status parameter may include, but is not limited to, an error when a burst with an illegal size and correct LLRC was received as part of this packet.

Issued – The HIPPI-PH shall issue this primitive to the Destination ULP when it receives a packet boundary indication.

Effect - Unspecified

# 4.8.4 PH\_PACKET.Response

This primitive acknowledges the PH\_PACKET.Indicate from the HIPPI-PH.

Semantics - PH\_PACKET.Response

Issued – The Destination ULP issues this primitive to acknowledge receipt of the PH\_PACKET.Indicate.

Effect – The HIPPI-PH is enabled to issue another PH\_PACKET.Indicate.

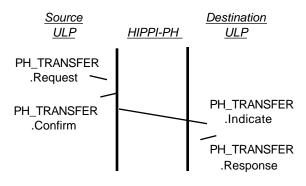

#### 4.9 Data transfer service primitives

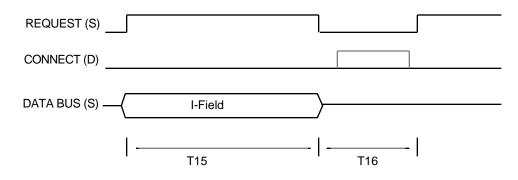

Figure 8 is a diagram of these primitives. They shall be used to transfer a burst from the Source ULP to the Destination ULP.

Figure 8 – Data transfer service primitives

#### 4.9.1 PH\_TRANSFER.Request

This primitive is issued by the Source ULP to request the transfer of a burst.

Semantics - PH\_TRANSFER.Request (Length,Burst)

The length parameter may be specified in any units, but an integral number of words shall be transferred.

Issued – The Source ULP issues this primitive to the HIPPI-PH to request the transfer of a burst to the Destination ULP.

Effect – The HIPPI-PH shall accept the burst for transmission.

#### 4.9.2 PH\_TRANSFER.Confirm

This primitive acknowledges the PH\_TRANSFER.Request from the Source ULP.

Semantics - PH\_TRANSFER.Confirm (Accept/Reject)

The parameter denotes whether or not the primitive was accepted by the HIPPI-PH.

Issued – The HIPPI-PH shall issue this primitive to the Source ULP to acknowledge a PH\_TRANSFER.Request.

Effect - Unspecified

#### 4.9.3 PH\_TRANSFER.Indicate

This primitive indicates to the Destination ULP that a burst has been received from the Source ULP.

Semantics – PH\_TRANSFER.Indicate (Status,Length, Burst)

The Status parameter reports any parity or LLRC errors detected during the data transfer if error checking is supported. Illegal length bursts, with correct LLRC, shall be indicated in the PH\_PACKET.Indicate primitive if error checking is supported.

Issued – The HIPPI-PH shall issue this primitive to the Destination ULP when a burst has been received.

Effect - Unspecified

#### 4.9.4 PH\_TRANSFER.Response

This primitive acknowledges the PH\_TRANSFER.Indicate from the HIPPI-PH.

Semantics - PH\_TRANSFER.Response

Issued – The Destination ULP issues this primitive to acknowledge receipt of the PH\_TRANSFER.Indicate.

Effect – The HIPPI-PH is enabled to issue another PH\_TRANSFER.Indicate.

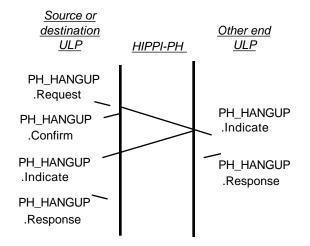

#### 4.10 Hangup service primitives

Figure 9 is a diagram of these primitives. They shall be used to terminate a connection between the Source and Destination. Note that a Hangup can be initiated from either the Source or Destination and will usually affect both the local and opposite ends of the interface.

Figure 9 – Hangup service primitives

#### 4.10.1 PH\_HANGUP.Request

This primitive is issued by either the Source ULP or Destination ULP to request that the connection be terminated.

Semantics - PH\_HANGUP.Request

Issued – The Source ULP or Destination ULP issues this primitive to the HIPPI-PH to terminate a connection.

Effect - The HIPPI-PH shall terminate the connection.

X3T9.3 maintenance copy of ANSI X3.183-1991

#### 4.10.2 PH\_HANGUP.Confirm

This primitive acknowledges the PH\_HANGUP.Request to the issuing ULP.

Semantics – PH\_HANGUP.Confirm

Issued – The HIPPI-PH shall issue this primitive to the ULP to acknowledge a PH\_HANGUP.Request.

Effect - Unspecified

#### 4.10.3 PH\_HANGUP.Indicate

This primitive indicates to the ULP that the connection has been terminated. If a connection exists, the ULP that issued the PH\_HANGUP.Request shall receive a PH\_HANGUP.Confirm when the hangup sequence starts and a PH\_HANGUP.Indicate when the sequence completes. The other end ULP shall receive only a PH\_HANGUP.Indicate.

Semantics - PH\_HANGUP.Indicate

Issued – The HIPPI-PH shall issue this primitive to the ULP when the connection has been terminated.

Effect – The ULP may no longer use the connection for data transfers, and all pending .Requests are cancelled.

#### 4.10.4 PH\_HANGUP.Response

This primitive acknowledges the PH\_HANGUP.Indicate from the HIPPI-PH.

Semantics – PH\_HANGUP.Response

Issued – The ULP issues this primitive to acknowledge receipt of the PH\_HANGUP.Indicate.

Effect – The HIPPI-PH is enabled to issue another PH\_HANGUP.Indicate.

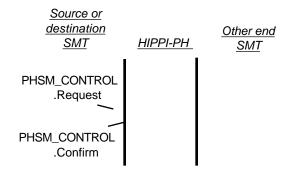

# 4.11 Control service primitives

Figure 10 shows the SMT Control service primitives. They shall be used to set parameters and control the interface. Note that a Control primitive can be initiated from either the Source or Destination.

Figure 10 - Control service primitives

#### 4.11.1 PHSM\_CONTROL.Request

This primitive is issued by either the Source SMT or Destination SMT to set parameters within the interface, start diagnostics, or otherwise control the interface. One function is specified and others are left to specific implementations.

Semantics – PHSM\_CONTROL.Request (Parameter\_List)

The Parameter\_List specifies what is to be set, started, etc. The Parameter list includes but is not limited to: Reset

Issued – The Source or Destination SMT issues this primitive to perform some control function over the interface as a whole.

Effect – The HIPPI-PH shall perform the function specified. The Reset parameter shall take the HIPPI-PH to the Disabled state and cancel all pending .Requests.

#### 4.11.2 PHSM\_CONTROL.Confirm

This primitive acknowledges the PHSM\_CONTROL.Request to the issuing SMT.

Semantics – PHSM\_CONTROL.Confirm (Status, Status\_ List)

Status reports the success or failure of the PHSM\_CONTROL.Request operation. There should be one status value in Status\_List for each event initiated with the PHSM\_CONTROL.Request.

Issued – The HIPPI-PH shall issue this primitive to the SMT when all of the operations specified in the PHSM\_CONTROL.Request have been accepted or completed.

Effect - Unspecified

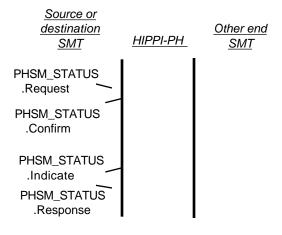

# 4.12 Status service primitives

Figure 11 shows the SMT Status service primitives. They shall be used to obtain local status information from the HIPPI-PH. Note that a Status primitive can be initiated from either the Source or Destination and shall only affect the local end of the interface.

Figure 11 – Status service primitives

# 4.12.1 PHSM\_STATUS.Request

This primitive is issued by either the Source SMT or Destination SMT to request a status report from the HIPPI-PH.

Semantics - PHSM\_STATUS.Request

Issued – The SMT issues this primitive to the HIPPI-PH when it wishes to obtain the status of the interface.

Effect – The HIPPI-PH shall respond with a PHSM\_STATUS.Confirm.

#### 4.12.2 PHSM\_STATUS.Confirm

This primitive replies to the previous PHSM\_STATUS.Request with status information.

Semantics – PHSM\_STATUS.Confirm (Status)

```

Status shall contain, but is not limited to:

INTERCONNECT state

Errors

```

Issued – The HIPPI-PH shall issue this primitive to the SMT to acknowledge a PHSM\_STATUS.Request.

Effect - Unspecified

#### 4.12.3 PHSM\_STATUS.Indicate

This primitive informs the SMT entity that a major event has occurred that affects the operation of the HIPPI-PH.

Semantics - PHSM\_STATUS.Indicate

Issued – The HIPPI-PH shall issue this primitive to the SMT whenever a major event is detected. Major events include but are not limited to a change in the INTERCONNECT signal.

NOTE – If a PHSM\_CONTROL.Request was accepted successfully but not completed, then an PHSM\_STATUS.Indicate could be used to indicate completion.

Effect – Upon receipt of this primitive, the local SMT entity should issue a PHSM\_STATUS.Request to read the status of the HIPPI-PH and determine which event occurred.

#### 4.12.4 PHSM\_STATUS.Response

This primitive acknowledges the PHSM\_STATUS.Indicate from the local SMT entity.

Semantics - PHSM\_STATUS.Response

Issued – The SMT issues this primitive to acknowledge receipt of the PHSM\_STATUS.Indicate.

Effect – The HIPPI-PH is enabled to issue another PHSM\_STATUS.Indicate.

# 5 Interface format and signals

# 5.1.1 Connections

Connections shall be delimited by both the REQUEST and CONNECT signals being true.

# 5.1 Physical framing hierarchy

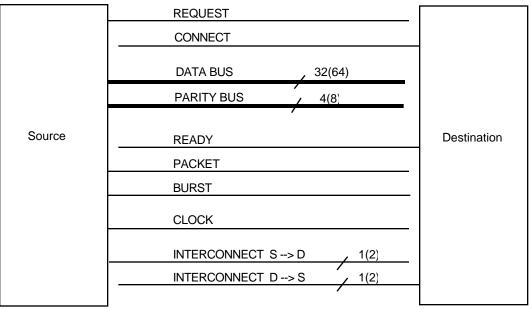

Information shall be transferred across the HIPPI-PH as shown in figure 12. The interface signals are illustrated in figure 13.

Figure 12 – Physical framing hierarchy

(Numbers in parentheses are for 1600 Mbit/s option)

Figure 13 – Interface signal summary

#### 5.1.2 I-Field

The I-Field shall be delimited by the REQUEST signal being asserted and the CONNECT signal going true. The 32-bit I-Field may be used to supply non-specified control information when a connection is made. The I-Field timing is described in 7.5.

DATA BUS signals D00 through D31, on Cable-A, shall be used for the I-Field. The other signals of the word, if any, shall be zeros. Parity shall be correct for all bytes.

#### 5.1.3 Packets

Packets shall be delimited by the PACKET signal being true. Once a connection has been established, a packet, or multiple packets, may be transferred from the Source to the Destination. Packets shall be composed of one or more bursts. For descriptive purposes only, packets are organized into classes based on the order of short bursts and full bursts.

Class 1 shall include all packets which are composed of a single short burst.

Class 2 shall include all packets which are composed of a short burst followed by one or more full bursts.

Class 3 shall include all packets which are composed of one or more full bursts followed by a short burst.

Class 4 shall include all packets which are composed of one or more full bursts and no short bursts.

#### 5.1.4 Bursts

Bursts shall be delimited by the BURST signal being true. Bursts shall consist of a group of words sent on the DATA BUS, one word per CLOCK period, during contiguous clock periods. Bursts shall contain 1 to 256 words. Bursts that contain less than 256 words are called short bursts. A packet shall contain no more than one short burst. A short burst shall be either the first or last burst of a multi-burst packet.

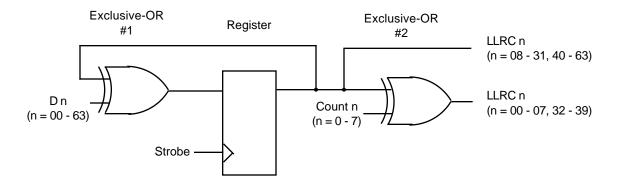

#### 5.1.5 LLRC

A length/longitudinal redundancy checkword (LLRC) shall be sent from the Source to the Destination on the DATA BUS during the first clock period following the burst. See annex C for an example LLRC calculation.

For data signals D00-D31, the LLRC value in data signal position n is defined as:

$$L_n = \left(\sum_{j=1}^{B} D_{nj}\right) + S_n$$

where

B is the number of words in the burst;

D<sub>ni</sub> is the bit value in position n of word i of the burst;

$S_n$  is the value of seed in position *n* where the seed is defined as B modulo 256.

All addition is modulo 2.

When the 1600-Mbit/s option is used the LLRC value in data signal position *n*, for data signals D32-D63, is defined as:

$$L_n = \left(\sum_{i=1}^{B} D_{n_i}\right) + S(n - 32)$$

where  $S_{(n-32)}$  is the value of the seed in position (n - 32) where the seed is defined as B modulo 256

All addition is modulo 2.

#### 5.1.6 Wait time

The amount of wait time between packets and bursts may vary. The minimum wait times are specified in 7.8. Maximum wait times depend on the data flow to or from the upper-layer protocols and on the data flow to or from the opposite end of the interface. The contents of the DATA BUS and PARITY BUS are undefined during wait times.

#### 5.2 Data rate options

The HIPPI-PH supports peak data rates of 800 and 1600 Mbit/s. These different data rates shall be achieved by using different widths for the DATA BUS. Table 1 summarizes the data rate options.

| Table | 1 – | Data | rate | options |

|-------|-----|------|------|---------|

|-------|-----|------|------|---------|

| Peak Data Ra<br>(Mbit/s              |    |      |      |

|--------------------------------------|----|------|------|

|                                      |    | 800  | 1600 |

| Width of DATA BUS (bits)             |    | 32   | 64   |

| Word size (bits)                     |    | 32   | 64   |

| Width of PARITY BUS (bits)           |    | 4    | 8    |

| Size of I-Field (bits)               |    | 32   | 32   |

| Maximum size of burst (bytes)        |    | 1024 | 2048 |

| Number of cables per simplex interfa | се | 1    | 2    |

#### 5.3 Usage of signals

Signal levels are "asserted" or "deasserted" at the driving end and "true" or "false" at the receiving end. The signal levels are more fully defined in 8.1.4.

#### 5.3.1 INTERCONNECT

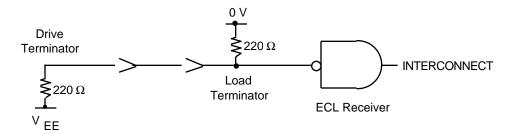

The INTERCONNECT signals shall indicate to both the Source and the Destination that the associated cable(s) are connected and that the other end is powered up. INTER-CONNECT false means that all other signals are invalid. One wire-pair in each cable shall be used for the INTER-CONNECT signals. The INTERCONNECT signals shall meet the electrical requirements described in 8.2. A recommended circuit for the INTERCONNECT signals is detailed in 8.2.

NOTE – It is recommended that the INTERCONNECT signal be sampled for multiple CLOCK times to insure that spurious noise does not cause false indications.

#### 5.3.1.1 With 800-Mbit/s option

When the 800-Mbit/s data rate option is used, there shall be two INTERCONNECT signals: INTERCONNECT-A Source to Destination and INTERCONNECT-A Destination to Source. In this standard, INTERCONNECT at the Source shall mean the INTERCONNECT-A Destination to Source signal. INTERCONNECT at the Destination shall mean the INTER-CONNECT-A Source to Destination signal.

#### 5.3.1.2 With 1600-Mbit/s option

When the 1600-Mbit/s data rate option is used, there shall be four INTERCONNECT signals: INTERCONNECT-A Source to Destination, INTERCONNECT-B Source to Destination, INTERCONNECT-A Destination to Source, and INTERCONNECT-B Destination to Source. The -A and -B specify the cable number.

In this standard, INTERCONNECT at the Source shall mean the "logical and" of INTERCONNECT-A Destination to Source and INTERCONNECT-B Destination to Source. INTERCONNECT at the Destination shall mean the "logical and" of INTERCONNECT-A Source to Destination and INTERCONNECT-B Source to Destination.

# 5.3.2 DATA BUS

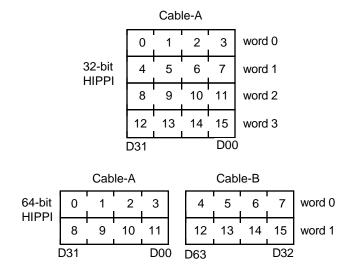

The DATA BUS shall consist of 32 or 64 signals labelled D00 through D31 or D00 through D63. As shown in table 2, D00 through D31 shall be in Cable-A, D32 through D63 shall be in Cable-B. The width of the DATA BUS controls the data rate of the HIPPI-PH as specified in table 1. The DATA BUS shall be used to transmit the I-Field, bursts, and LLRCs. The DATA BUS signals shall meet the timing requirements described in 7.3.

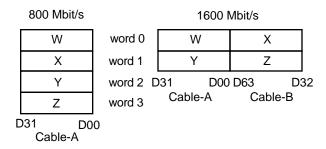

The data transferred between the ULP and the HIPPI-PH shall be 32-bit or 64-bit words, to match the HIPPI-PH DATA BUS width as defined in table 1. When mixing 32-bit and 64-bit systems and HIPPI-PHs, the data shall be packed as shown in figure 14. Clause B.6 describes the byte ordering within the words, which is specified by the HIPPI-FP framing protocol standard.

#### 5.3.3 PARITY BUS

The PARITY BUS shall implement odd parity for each byte transmitted on the DATA BUS. The PARITY BUS signals shall meet the timing requirements described in 7.3. See annex C for an example calculation.

The transverse (byte) parity signal in position n for each word is defined as:

$$P_n = \left(\sum_{i=0}^{7} D_{8n+i}\right) + 1$$

where

*n* is the signal position on the PARITY BUS;

$D_{8n+i}$  is the signal position on the DATA BUS.

All addition is modulo 2.

#### 5.3.4 REQUEST

The REQUEST signal shall be asserted by the Source to notify the Destination that a connection is desired. The Source shall begin asserting the REQUEST signal only when the CONNECT signal is false. REQUEST shall remain asserted for the duration of the connection.

REQUEST shall be accompanied by an I-Field on the DATA BUS. The I-Field shall meet the specifications described in 5.1.2 and the timing requirements described in 7.5.

An aborted connection sequence occurs when the Source deasserts the REQUEST signal before sensing that the CONNECT signal has changed from false to true. After an aborted connection sequence, the Source shall wait for a time equivalent to the round-trip propagation delay between the Source and Destination, including the time required by any transparent line extension devices in the path, before reasserting REQUEST to start another connection sequence.

REQUEST shall be deasserted when INTERCONNECT is false or when CONNECT makes a transition from true to false. REQUEST may be deasserted by the Source at any time to indicate to the Destination that the connection is no longer available.

Once REQUEST is deasserted, the Source shall not reassert REQUEST until CONNECT is in the false state.

When REQUEST is false, the Destination shall assume that no other signals asserted by the Source, except CLOCK and INTERCONNECT, are valid.

The REQUEST signal shall meet the timing requirements described in 7.4.

#### 5.3.5 CONNECT

The CONNECT signal shall be asserted by the Destination in response to a REQUEST. CONNECT notifies the Source that the Destination is available for data transfers. CONNECT shall remain asserted for the duration of the connection. When both REQUEST and CONNECT are true, a Connection is said to be established or available.

CONNECT shall not be asserted unless both INTERCON-NECT and REQUEST are true. The Destination shall not assert CONNECT until it is acceptable to have the I-Field removed from the DATA BUS. A rejected connection sequence occurs when the Destination asserts the CONNECT signal for at least four but no more than 16 CLOCK periods. The Destination shall not generate any READY indications during the rejected connection sequence.

CONNECT shall be deasserted if either INTERCONNECT or REQUEST is false. Once a connection has been established CONNECT may be deasserted by the Destination at any time to indicate to the Source that the connection is no longer available. Once CONNECT is deasserted, the Destination shall not reassert CONNECT until REQUEST has been received in the false state and returns to the true state.

When CONNECT is false, the Source shall assume that no other signals asserted by the Destination, except INTER-CONNECT, are valid. The CONNECT signal shall meet the timing requirements described in 7.7.

# 5.3.6 READY

READY indications may be sent by the Destination after a connection is established, i.e., after CONNECT is asserted. A Destination shall send one READY indication for each burst that it is prepared to accept from the Source. This burst look-ahead function may be implemented in the Destination to minimize the effect of loop propagation delays that would otherwise slow throughput on long cables.

For each READY indication received, the Source has permission to send one burst. All Sources shall accept a minimum of 63 look-ahead READY indications.

The Destination shall deassert READY when CONNECT is deasserted.

Before a connection is established, the READY counts shall be cleared in both the Source and Destination.

The READY signal shall meet the timing requirements described in 7.7.

#### NOTES

1 – With the burst look-ahead function, the Destination controls the flow by enabling as many bursts as it can accept in its buffer memory. As long as the READY indications arrive at the Source before the Source is ready to send the next burst, there will be no time lost between bursts. Bursts of 256 words require about one burst buffer for each km of cable distance.

2 – Errors may cause READY indications to be lost. This can cause performance degradation or deadlock of the interface until a higher layer requests a hangup and a reconnect. For this reason, implementors should restrict the length of time that a connection is held depending on the error characteristics of the link.

# 5.3.7 PACKET

The PACKET signal is a delimiter asserted by the Source to mark a group of bursts as a packet. The PACKET signal shall be asserted before the first burst and shall remain asserted until after the final burst of the packet.

The PACKET signal shall be deasserted when REQUEST is deasserted.

The PACKET signal shall meet the timing requirements described in 7.4, 7.8, and 7.9.

#### 5.3.8 BURST

The BURST signal is a delimiter marking a group of words on the DATA BUS as a burst. The BURST signal shall be asserted by the Source with the first word of the burst and shall remain asserted for all subsequent words of the burst.

The BURST signal shall be deasserted when PACKET or REQUEST is deasserted.

The BURST signal shall meet the timing requirements described in 7.4, 7.8, and 7.9.

# 5.3.9 CLOCK

The CLOCK signal shall be a symmetrical signal with a period of 40 ns (i.e., a frequency of 25 MHz). CLOCK shall be provided by the Source and shall run continuously. The CLOCK signal shall meet the timing requirements described in 7.1 and 7.2.

# 5.4 Error detection

#### 5.4.1 Parity

Odd byte parity shall be transmitted on the PARITY BUS with each byte transmitted on the DATA BUS. This includes the I-Field, each word of every burst, and the LLRC.

#### 5.4.2 LLRC

An LLRC, as specified in 5.1.5, shall be transferred across the DATA BUS during the first CLOCK period following each burst.

#### 5.4.3 Destination error checking

The Destination is not required to check for any errors.

#### 5.4.4 Recovery

The HIPPI-PH is a simplex point-to-point interface, therefore, retransmissions and error status reports from the Destination to the Source are beyond the scope of this standard.

# 6 State transitions

The HIPPI-PH service primitives and physical signals are tied together by the state transition pseudo-code and flow diagrams of this clause. The flow diagrams are included as a convenience and are not a rigorous definition.

The state transitions and flow diagrams do not describe the means or specific implementation by which the functions are provided. However, other implementations with fewer or additional states shall behave in a manner which is compatible with peer protocols implemented identical to the model.

Source states start with the letter S, Destination states with the letter D. Source states within this standard are numbered 1Jx0 where J = 0 - 4. Destination states within this document are numbered 1Kx0 where K = 5 - 9. This numbering scheme is used to avoid confusion between the Source and Destination states, and between states in this document and states in the data framing layer.

# 6.1 State exit

Within a state that is testing for some condition, the pseudo-code is assumed to loop indefinitely within the state until some exit condition is met. There is no prescribed order for testing the conditions except that the change in INTERCONNECT an asynchronous event. INTERCONNECT going false takes the Source to S1160, and the Destination to D1660.

In the event that control sequence errors are detected, the Destination shall go to D1600. For purposes of reporting errors, control sequence errors take precedence over parity or LLRC errors. Control sequence errors include violations of 5.3, 7.8 and 7.9.

# 6.2 Interlocks

The implementor is cautioned that interlock flags or queues may be necessary to enforce the requirement of 4.1 that a second .Indicate primitive may not be issued by the HIPPI-PH until a .Response primitive of the same name has been received from the ULP. These interlocks are not illustrated in the pseudo-code.

# 6.3 Source READY pseudo-code

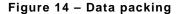

The Source READY flow diagram in figure 15 gives an overview of the Source READY pseudo-code. The S\_READY\_Ctr counts READY indications received from the Destination. Each READY indication gives the Source permission to send a burst. The Source decrements the S\_READY\_Ctr for each burst it sends to the Destination.

#### 6.3.1 SR1000

Initialize the S\_READY\_Ctr. Enter on Power-up, Master Reset, or when the connection is broken.

Reset S\_READY\_Ctr Goto SR1010

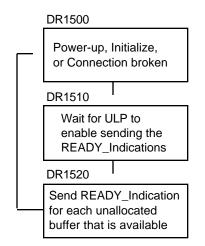

Figure 15 – Source READY flow diagram

#### 6.3.2 SR1010

Wait for the S\_READY\_Ctr to be enabled by the Source pseudo-code S1190.

IF S\_READY\_Enable = set THEN Goto SR1020

# 6.3.3 SR1020

Count READY indications received from the Destination.

IF READY\_Indication THEN Increment S\_READY\_Ctr IF S\_READY\_Enable = reset THEN Goto SR1000

#### 6.4 Destination READY pseudo-code

The Destination READY flow diagram in figure 16 gives an overview of the Destination READY pseudo-code. Each READY indication issued gives the Source permission to send a burst.

Figure 16 – Destination READY flow diagram

# 6.4.1 DR1500

Initialize the circuitry that keeps track of the available burst buffers in the Destination. Enter on Power-up, Master Reset, or when the connection is broken.

Deassert READY Reset Available\_Buffers\_Logic Goto DR1510

# 6.4.2 DR1510

Wait for the Destination pseudo-code D1690 to enable sending READY indications. The connection must be accepted with CONNECT true before sending READY indications.

IF D\_READY\_Enable = set THEN Goto DR1520

#### 6.4.3 DR1520

Send READY indications as buffers are freed up.

- IF Unallocated Burst Buffer is Available

- THEN Issue READY\_Indication

- IF D\_READY\_Enable = reset THEN Goto DR1500

#### 6.5 Source pseudo-code

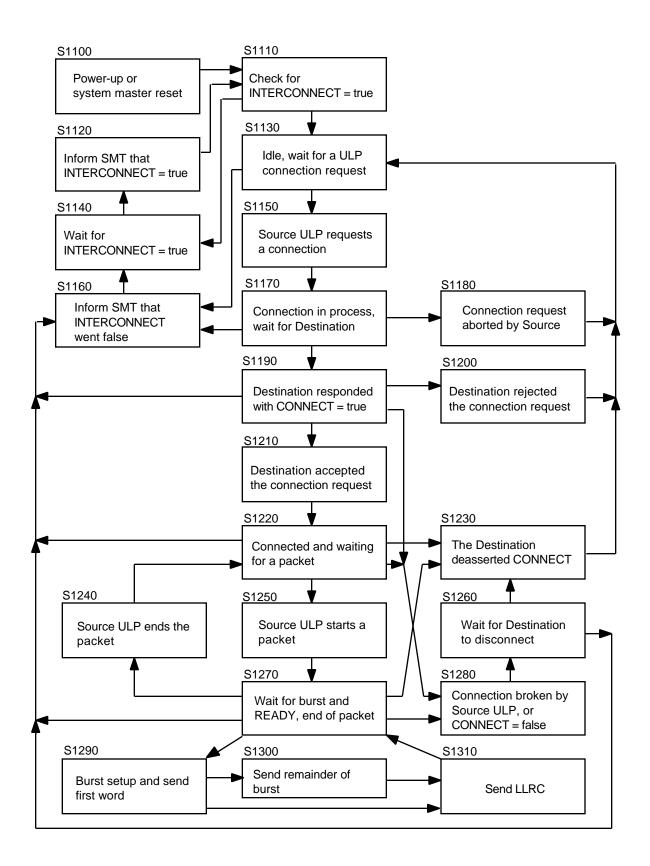

The Source flow diagram in figure 17 gives an overview of the Source pseudo-code.

#### 6.5.1 S1100

Disabled state; initialize the HIPPI-PH and relevant local state variables. Enter on Power-up or system master reset.

Deassert BURST Deassert PACKET Deassert REQUEST Reset S\_READY\_Enable Goto S1110

#### 6.5.2 S1110

Check the INTERCONNECT signal from the Destination. Wait for old REQUEST and CONNECT signals to die out on the cable during time T1 (see 4.5.1).

IF INTERCONNECT = false THEN Goto S1140 Wait time T1 Goto S1130

# 6.5.3 S1120

Inform the Source SMT that the INTERCONNECT signal has gone to the true state.

Issue PHSM\_STATUS.Indicate Goto S1110

#### 6.5.4 S1130

Idle state; the interface is available, but not connected. Wait for the Source ULP to request a connection.

IF INTERCONNECT = false THEN Goto S1160 IF PH\_RING.Request (CCI) AND IF CONNECT = false THEN Goto S1150 ; Start connection

#### 6.5.5 S1140

Wait for the INTERCONNECT signal to go true.

IF INTERCONNECT = true THEN Goto S1120

# 6.5.6 S1150

The Source ULP has requested that a connection sequence be started. Use the information in the Source ULP CCI parameter as the I-Field.

Issue PH\_RING.Confirm Assert CCI on DATA BUS as I-Field Assert REQUEST Goto S1170

#### 6.5.7 S1160

Inform the Source SMT that the INTERCONNECT signal has gone false.

Deassert BURST Deassert PACKET Deassert REQUEST Reset S\_READY\_Enable Issue PHSM\_STATUS.Indicate Goto S1140

#### 6.5.8 S1170

A connection sequence is in process. Wait for the Destination to complete the connection, either accepted or rejected, or for the Source ULP to abort the connection request.

IF INTERCONNECT = false THEN Goto S1160 IF PH\_HANGUP.Request THEN Goto S1180 ; Abort connection IF CONNECT = true THEN Goto S1190 ; Connection completed

#### 6.5.9 S1180

The connection is being aborted by the Source ULP before the Destination has completed the connection, i.e., the CONNECT signal has not been received. Time T1, as defined in 4.5.1, allows the REQUEST and CONNECT signals to propagate and settle before allowing another connection request sequence.

Deassert REQUEST Issue PH\_HANGUP.Confirm Reset S\_READY\_Enable Wait time T1 Goto S1130

# 6.5.10 S1190

The Destination has responded with the CONNECT signal true. Wait for the CONNECT signal to be true for at least 17 CLOCK periods, or receiving a READY indication, before signalling that the connection has been accepted. The Destination may reject this connection request by asserting CONNECT for a time between 4 and 16 CLOCK periods and then deasserting CONNECT.

Set S\_READY\_Enable IF INTERCONNECT = false THEN Goto S1160 IF PH\_HANGUP.Request THEN Goto S1280 ; Abort connection IF CONNECT = false THEN Goto S1200 ; Connection rejected IF S\_READY\_Ctr > 0 THEN Goto S1210 ; Connection accepted IF CONNECT = true AND 17 CLOCK periods have expired THEN Goto S1210 ; Connection accepted

#### 6.5.11 S1200

Inform the Source ULP that the Destination has rejected the connection by deasserting CONNECT before sending a READY indication.

Issue PH\_ANSWER.Indicate (Reject) Deassert REQUEST Reset S\_READY\_Enable Goto S1130

# 6.5.12 S1210

Inform the Source ULP that the connection has been established.

Issue PH\_ANSWER.Indicate (Accept) Goto S1220

# 6.5.13 S1220

The connection has been established and the interface is now available for packet transfers.

IF INTERCONNECT = false THEN Goto S1160 IF CONNECT = false THEN Goto S1230 ; Connection broken IF PH\_PACKET.Request (Begin) THEN Goto S1250 ; Start of packet IF PH\_HANGUP.Request THEN Goto S1280 ; Break connection

# 6.5.14 S1230

Inform the Source ULP that the Destination has broken the connection by deasserting CONNECT.

Issue PH\_HANGUP.Indicate Deassert PACKET Deassert REQUEST Reset S\_READY\_Enable Goto S1130

#### 6.5.15 S1240

The Source ULP has terminated a packet. Deassert the PACKET signal and acknowledge the ULP primitive.

Deassert PACKET Issue PH\_PACKET.Confirm (Accept) Goto S1220

#### 6.5.16 S1250

The Source ULP has started a packet. Assert the PACKET signal and acknowledge the ULP primitive.

Assert PACKET Issue PH\_PACKET.Confirm (Accept) Goto S1270

# 6.5.17 S1260

Wait for Source ULP breaking of the connection to be acknowledged by the Destination deasserting CONNECT.

IF INTERCONNECT = false THEN Goto S1160 IF CONNECT = false THEN Goto S1230 : Connection broken

#### 6.5.18 S1270

A packet has been started; wait for a burst from the Source ULP or an end of packet primitive. The Word\_Counter shall be used to count the number of words in the burst.

IF INTERCONNECT = false THEN Goto S1160 IF CONNECT = false THEN Goto S1230 : Connection broken IF PH PACKET.Request (End) THEN Goto S1240 ; End of packet IF PH\_HANGUP.Request THEN Goto S1280 : Break connection Reset Word\_Counter Reset LLRC calculation IF PH\_TRANSFER.Request (Length, Burst) AND IF S\_READY\_Ctr > 0 THEN Goto S1290

#### 6.5.19 S1280

Break the connection from the Source end. The connection was completed, i.e., a PH\_ANSWER.Indicate (Accept) has been issued.

Deassert REQUEST Deassert PACKET Reset S\_READY\_Enable Issue PH\_HANGUP.Confirm Goto S1260

### 6.5.20 S1290

There is a burst to transfer and a READY indication available. Acknowledge the burst primitive, decrement the READY counter, and send the first word.

Convert Length to words Initialize LLRC with Length Issue PH\_TRANSFER.Confirm (Accept) Decrement S\_READY\_Ctr Assert BURST Assert first word of burst on DATA BUS Accumulate LLRC Count CLOCK period in Word\_Counter IF Word\_Counter = Length THEN Deassert BURST Goto S1310 Goto S1300

# 6.5.21 S1300

Send the remainder of the burst to the Destination.

Assert words of burst on DATA BUS Accumulate LLRC Count CLOCK periods in Word\_Counter IF Word\_Counter = Length THEN Deassert BURST Goto S1310

# 6.5.22 S1310

Send the LLRC associated with the previous burst to the Destination.

Assert LLRC on DATA BUS Goto S1270

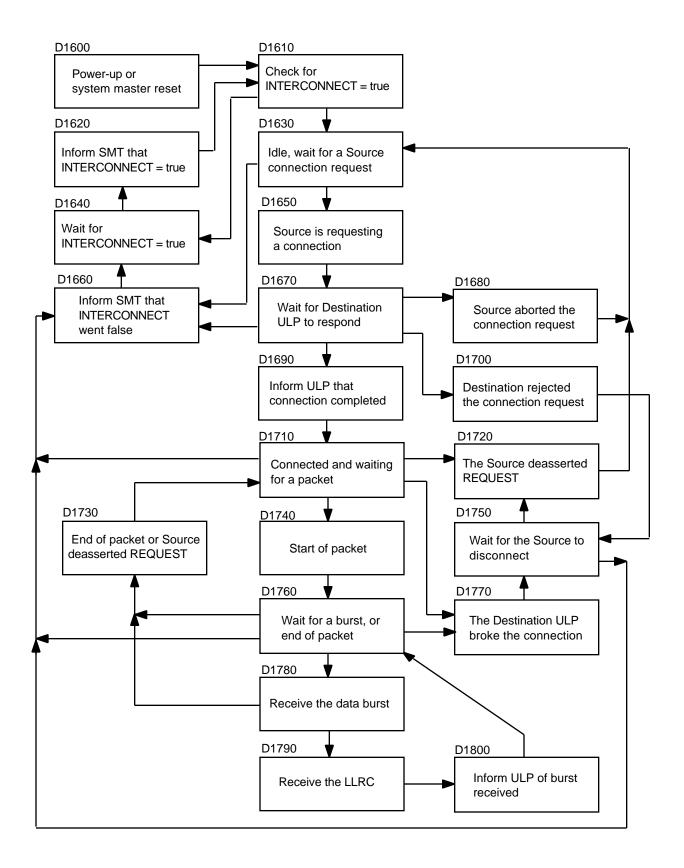

#### 6.6 Destination pseudo-code

The Destination flow diagram in figure 18 gives an overview of the Destination pseudo-code.

#### 6.6.1 D1600

Disabled state; initialize the HIPPI-PH and relevant local state variables. Enter on Power-up or system master reset.

Reset D\_READY\_Enable Deassert CONNECT Goto D1610

#### 6.6.2 D1610

Check the INTERCONNECT signal from the Source. Wait for any previous connection attempts to be terminated, i.e., REQUEST = false.

IF INTERCONNECT = false THEN Goto D1640 IF REQUEST = false THEN Goto D1630

# 6.6.3 D1620

Inform the Destination SMT that the INTERCONNECT signal has gone to the true state.

Issue PHSM\_STATUS.Indicate Goto D1610

#### 6.6.4 D1630

Idle state; the interface is available but not connected. Wait for the Source to request a connection.

IF INTERCONNECT = false THEN Goto D1660 IF REQUEST = true THEN Goto D1650 ; Connection request

#### 6.6.5 D1640

Wait for the INTERCONNECT signal to be true.

IF INTERCONNECT = true THEN Goto D1620

#### 6.6.6 D1650

The Source has requested a connection. Use the information in the I-Field as the CCI parameter passed to the Destination ULP. Note that this CCI may be different from the CCI supplied by the PH\_RING.Request primitive (in 6.5.6 S1150) due to the action of intermediate devices, such as switches, between the Source and Destination.

Issue PH\_RING.Indicate (CCI) Goto D1670

#### 6.6.7 D1660

Inform the Destination SMT that the INTERCONNECT signal has gone false.

Reset D\_READY\_Enable Deassert CONNECT Issue PHSM\_STATUS.Indicate Goto D1640

#### 6.6.8 D1670

A connection sequence is in process. Wait for the Destination ULP to complete the connection, either accepted or rejected, or for the Source to abort the connection request.

- IF INTERCONNECT = false THEN Goto D1660

- IF REQUEST = false

- THEN Goto D1680 ; Connection request aborted IF PH ANSWER.Request (Accept)

- THEN Goto D1690 ; Connection accepted IF PH\_ANSWER.Request (Reject)

- THEN Goto D1700 ; Connection rejected

#### 6.6.9 D1680

The connection is being aborted from the Source end before the Destination has completed the connection.

Issue PH\_HANGUP.Indicate Goto D1630

#### 6.6.10 D1690

Inform the Destination ULP that the connection has been completed.

Issue PH\_ANSWER.Confirm Assert CONNECT Set D\_READY\_Enable Goto D1710

Figure 18 – Destination flow diagram

# 6.6.11 D1700

The Destination rejects the connection by asserting the CONNECT signal for a period of between 4 and 16 CLOCK periods and then deasserting CONNECT.

Issue PH\_ANSWER.Confirm Assert CONNECT Wait 4 to 16 CLOCK periods Deassert CONNECT Goto D1750

# 6.6.12 D1710

The connection has been established and the interface is now available for packet transfers.

IF INTERCONNECT = false THEN Goto D1660 IF REQUEST = false THEN Goto D1720 ; Source broke connection IF PACKET = true THEN Goto D1740 ; Start of packet IF PH\_HANGUP.Request THEN Goto D1770 ; Break connection

# 6.6.13 D1720

Inform the Destination ULP that the Source has deasserted REQUEST.

Issue PH\_HANGUP.Indicate Reset D\_READY\_Enable Deassert CONNECT ; If asserted Goto D1630

#### 6.6.14 D1730

Inform the Destination ULP that the Source has ended the packet.

Issue PH\_PACKET.Indicate (End, Status) Goto D1710

#### 6.6.15 D1740

Inform the Destination ULP that the Source has started a packet.

Issue PH\_PACKET.Indicate (Begin) Goto D1760

### 6.6.16 D1750

Wait for the Destination ULP breaking of the connection to be acknowledged by the Source deasserting REQUEST.

IF INTERCONNECT = false

THEN Goto D1660

- IF REQUEST = false

- THEN Goto D1720 ; Source broke connection

# 6.6.17 D1760

A packet has been started; wait for another burst or an end of packet indication. The Word\_Counter shall be used to count the number of words in the burst.

IF INTERCONNECT = false THEN Goto D1660 IF REQUEST = false THEN Goto D1730 ; Source broke connection IF PACKET = false THEN Goto D1730 ; End of packet IF PH\_HANGUP.Request THEN Goto D1770 ; Break connection Reset Word\_Counter Reset LLRC calculation IF BURST = true THEN Goto D1780 : Receive burst

# 6.6.18 D1770

Break the connection from the Destination end.

Reset D\_READY\_Enable Deassert CONNECT Issue PH\_HANGUP.Confirm Goto D1750

#### 6.6.19 D1780

Receive the burst being sent from the Source.

Count CLOCK periods in Word\_Counter Receive a burst on the DATA BUS Check parity on each word Accumulate LLRC IF REQUEST = false THEN Set Status = Error for PH\_PACKET.Indicate Goto D1730 ; Source disconnect IF BURST = false THEN Goto D1790

#### 6.6.20 D1790

Receive the Source-generated LLRC for the burst. Receive LLRC on DATA BUS Goto D1800

#### 6.6.21 D1800

Inform the Destination ULP that the burst has been received. The Word\_Counter shall be used to derive the Length parameter.

Issue PH\_TRANSFER.Indicate (Status,Length, Burst) Goto D1760

# 7 Timing

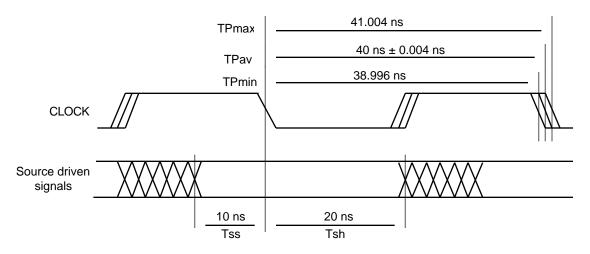

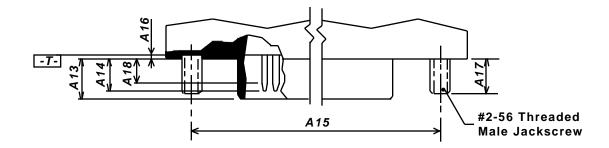

Unless otherwise specified, all parameters shall be measured at the bulkhead connector of the Source or Destination equipment. Specifications shall be met when operating with a maximum length cable, as specified in 8.5, and terminated as specified in 8.1.3.

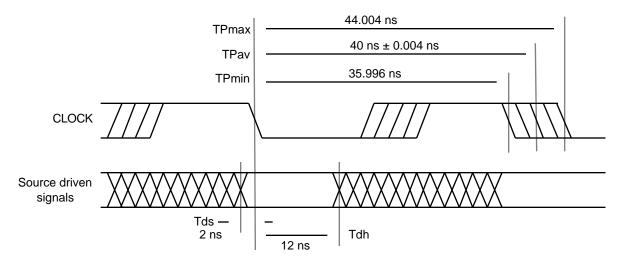

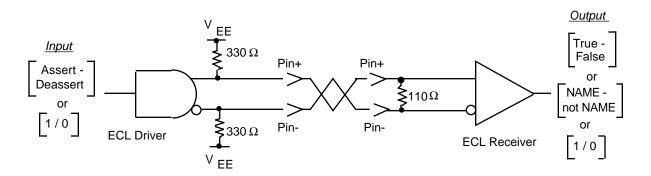

Example timing waveforms are shown in figure 19 and figure 20. The falling edge of a signal is defined as the Pin+ side of the differential pair, as shown in figure 20, going from the more-positive level to the less-positive level. Time intervals for differential signals are measured from the cross-over point where the differential voltage is zero.

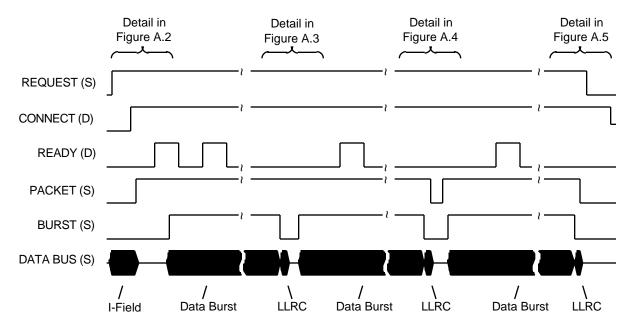

Annex A contains waveform examples.

# 7.1 Source CLOCK signal

The transmitted CLOCK signal at the Source bulkhead connector, as shown in figure 19, shall have a nominal period TPav of 40 ns  $\pm$  0.004 ns ( $\pm$  0.01 %).